# Effect of Top-Gate Dielectric Deposition on the Performance of Indium Tin Oxide Transistors

Sumaiya Wahid<sup>®</sup>, *Graduate Student Member, IEEE*, Alwin Daus<sup>®</sup>, *Member, IEEE*, Jimin Kwon<sup>®</sup>, *Member, IEEE*, Shengjun Qin<sup>®</sup>, *Student Member, IEEE*, Jung-Soo Ko, H.-S. Philip Wong<sup>(D)</sup>, Fellow, IEEE, and Eric Pop<sup>(D)</sup>, Fellow, IEEE

Abstract—We report ultrathin (~4 nm) channel indium tin oxide (ITO) transistors, comparing different precursors for atomic layer deposition (ALD) of the Al<sub>2</sub>O<sub>3</sub> top-gate dielectric, and analyze the role of dielectric deposition on transistor performance and gate bias stress stability. Waterbased ALD leads to very negative threshold voltage ( $V_T$ ), with devices remaining in the on-state. In contrast, both ozone and O<sub>2</sub>-plasma precursors yield devices that can turn off, but ozone-based ALD devices have less negative  $V_{\rm T}$  shift at short channel lengths, and relatively more positive  $V_{T}$  at all channel lengths. We achieve maximum drive current,  $I_{max} \approx 260 \ \mu A/\mu m$  at  $V_{DS} = 1$  V, on/off current ratio of >10<sup>10</sup> (limited by the instrument's noise floor) for  $L \approx 700$  nm ozone-Al<sub>2</sub>O<sub>3</sub> top-gated transistors. Across multiple devices, the effective mobility is  $\sim$ 42 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and contact resistance is ~376  $\Omega \cdot \mu$ m. The transistors also show good gate bias stability with normalized V<sub>T</sub> shift of +0.12 V(MV/cm)<sup>-1</sup> at gate stress field >3 MV/cm, a  $\sim$ 3x improvement vs. our previous reports of uncapped ITO transistors.

Index Terms-ITO, transistors, atomic layer deposition, effective mobility, contact resistance, bias stress stability.

## I. INTRODUCTION

XIDE semiconductors are compatible with back-end-of-Unite (BEOL) processing ( $\leq 500$  °C) [1] and monolithic three-dimensional (3D) integration due to their large-scale, low-temperature deposition methods [2], [3], [4], [5]. They are promising candidates as channel materials for field-effect

Manuscript received 5 January 2023; revised 31 March 2023; accepted 3 April 2023. Date of publication 6 April 2023; date of current version 23 May 2023. This work was supported in part by the Stanford SystemX Alliance and in part by the Stanford Nanofabrication Facility (SNF) and Stanford Nano Shared Facilities (SNSF) through NSF under Award ECCS-2026822. The work of Sumaiya Wahid was supported by the Stanford Graduate Fellowship (SGF). The review of this letter was arranged by Editor H. G. Xing. (Corresponding authors: Sumaiya Wahid; Eric Pop.

Sumaiya Wahid, Shengjun Qin, Jung-Soo Ko, and H.-S. Philip Wong are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: swahid@stanford.edu).

Alwin Daus is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA, and also with the Chair of Electronic Devices, RWTH Aachen University, 52074 Aachen, Germany.

Jimin Kwon is with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA, and also with the Department of Electrical Engineering, Ulsan National Institute of Science and Technology (UNIST), Ulsan 44919, South Korea.

Eric Pop is with the Department of Electrical Engineering and the Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305 USA (e-mail: epop@stanford.edu).

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LED.2023.3265316.

Digital Object Identifier 10.1109/LED.2023.3265316

transistors (FETs), due to high drive currents and low off-state currents [2], [3], [6], [7]. Recently, ultra-short channel (~8 nm) 2.5 nm thin In<sub>2</sub>O<sub>3</sub> FETs have shown  $\sim$ 3 mA/ $\mu$ m drive currents, but they suffer from poor on/off current ratio  $<10^2$  [4]. On the other hand, indium gallium zinc oxide (IGZO) devices have demonstrated high on/off current ratio of  $\sim 10^{12}$  but lower on-state current  $\sim 6 \,\mu A/\mu m$  [5]. Among this family of materials, indium tin oxide (ITO) transistors have shown both good on- and off-state performance, with effective mobility  $\mu_{\rm eff} \sim 55 \ {\rm cm^2 V^{-1} s^{-1}}$  [2] and high on/off current ratio  $\sim 10^{11}$  [3], [8]. However, almost all ITO transistors have backgated (BG) structures with no channel encapsulation. Thus, the effect of top dielectric deposition on the performance and stability of ITO FETs remains unexplored.

In this work, we fabricate top-gated (TG) ITO transistors with three different precursors: H<sub>2</sub>O, O<sub>2</sub>-plasma, and ozone  $(O_3)$ , for atomic layer deposition (ALD) of the Al<sub>2</sub>O<sub>3</sub> TG dielectric. We compare the role of the TG dielectric deposition on device behavior, under DC measurements and positive gate bias stress. In doing so, we determine the optimum precursor for Al<sub>2</sub>O<sub>3</sub> top dielectric deposition on ITO channels, based on parameters like threshold voltage (V<sub>T</sub>), on/off current ratio, mobility, drive current, minimum subthreshold swing and  $V_{\rm T}$ stability.

#### **II. FABRICATION AND MEASUREMENT**

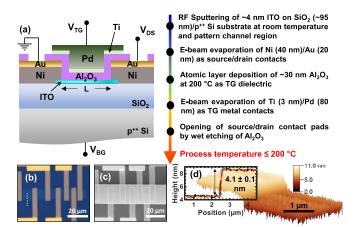

The cross-sectional schematic of a device along with the fabrication steps are shown in Fig 1(a). First, we deposit  $\sim$ 4 nm thick ITO channels by radio frequency (RF) magnetron sputtering on SiO<sub>2</sub> (95 nm)/p<sup>++</sup> Si substrates, which are used as global back-gates for initial BG measurements. The ITO deposition is done at room temperature with 100 W RF power, 5 mTorr deposition pressure, and 9:1 Ar:O<sub>2</sub> ratio. The channel region is patterned by lift-off or wet etching in diluted HCl (1.7%). Next, we e-beam evaporate and lift-off Ni (40 nm)/Au (20 nm) as source/drain contacts. For the TG dielectric, ALD of ~30 nm Al<sub>2</sub>O<sub>3</sub> film is done at 200 °C, with three different precursors: H<sub>2</sub>O, O<sub>2</sub>-plasma, and ozone (O<sub>3</sub>). Then, we e-beam evaporate and lift-off Ti (3 nm)/Pd (80 nm) as TG metal contact, before opening the source/drain contact pads by wet etching of Al<sub>2</sub>O<sub>3</sub>. The temperature remains  $\leq$  200 °C throughout all fabrication steps.

We fabricate transfer length method (TLM) structures with transistors of different channel lengths ( $L \sim 0.7, 1.6, 2.8, 4.7,$ 7.3, and 9.8  $\mu$ m). Figs. 1(b,c) show an optical and a scanning electron microscope image of a TLM before and after TG dielectric and metal deposition, respectively. Fig. 1(d) shows

0741-3106 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See https://www.ieee.org/publications/rights/index.html for more information. Authorized licensed use limited to: Stanford University. Downloaded on May 24,2023 at 18:38:47 UTC from IEEE Xplore. Restrictions apply.

(a) Schematic cross-section of the device structure and fabrication process flow of ITO transistors. (b) Optical image (before TG dielectric and metal deposition) and (c) scanning electron microscopy image (after TG dielectric and metal deposition) of transfer length method (TLM) structure. (d) Atomic force microscopy image across the green dotted line shown in (b); orange dashed line fitting the height profile (inset) shows the ITO channel thickness.

the atomic force microscopy profile across the green dotted line in Fig. 1(b), confirming the ITO thickness  $\sim 4$  nm. All electrical measurements were done at room temperature, in air, using a probe station with a Keithley 4200-SCS.

# **III. RESULTS AND DISCUSSION**

#### A. Back-Gated (BG) Measurements

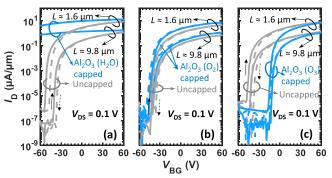

For initial analysis, we performed BG measurements using the p<sup>++</sup> Si substrate as a back-gate. The gray and blue curves in Fig. 2 show the BG transfer characteristics  $(I_D - V_{BG})$  of the uncapped and Al<sub>2</sub>O<sub>3</sub>-capped devices, respectively, for two channel lengths ( $L \sim 1.6 \ \mu m$  and 9.8  $\mu m$ ). The effect of ALD capping is shown with the three different precursors, H<sub>2</sub>O, O<sub>2</sub>, and O<sub>3</sub>, one in each panel of Fig. 2. The transfer curves for all uncapped, as-deposited samples are similar, with similar  $V_{\rm T}$ . After ALD of H<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub> the  $V_{\rm T}$  strongly shifts negatively, and the devices lose BG modulation [Fig. 2(a)]. This conductive channel could be caused by H-doping with residual H from the H<sub>2</sub>O precursor, or by the highly reactive trimethylaluminum precursor stripping off chemisorbed oxygen or -OH groups from the oxide channel, generating oxygen vacancies which donate free electrons [9], [10]. However, after O<sub>2</sub>-plasma and O<sub>3</sub>-based ALD, the transistors retain good BG modulation, suggesting passivation of oxygen vacancies or reintroduction of -OH groups into the channel, unlike H<sub>2</sub>Obased ALD [9]. For O<sub>2</sub>-plasma ALD,  $V_{\rm T}$  remains close to the as-deposited case [Fig. 2(b)], while  $O_3$ -ALD shifts the  $V_T$ positively, closer to 0 V [Fig. 2(c)]. A control experiment with the same number of *only* oxidant ( $O_2$  and  $O_3$ ) pulses revealed that both types of reactants shift the  $V_{\rm T}$  positively, and thus the duration, order, and number of O2 or O3 oxidant cycles may be tuned to achieve a desired  $V_{\rm T}$ .

## B. Top-Gated (TG) Measurements

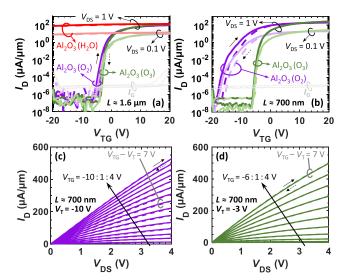

Fig. 3(a) shows the TG transfer characteristics  $(I_{\rm D}-V_{\rm TG})$ of 1.6  $\mu$ m devices with the three types of Al<sub>2</sub>O<sub>3</sub> as TG dielectric. As for the BG measurement, the H<sub>2</sub>O-precursor transistors show no TG modulation. On the other hand, O<sub>2</sub> and  $O_3$ -Al<sub>2</sub>O<sub>3</sub> devices are modulated by the TG (like the BG), but the  $O_2$ -plasma  $Al_2O_3$  device displays more negative  $V_{\rm T}$  (-1.1 V vs. 0.03 V) and degraded minimum subthreshold

Back-gated (BG) transfer characteristics for ITO transistors Fig. 2. (with L  $\sim$  1.6 and 9.8  $\mu$ m) before (gray) and after (blue) capping with Al<sub>2</sub>O<sub>3</sub> by ALD using (a) H<sub>2</sub>O, (b) O<sub>2</sub>-plasma, and (c) O<sub>3</sub> precursor. Solid and dashed small arrows indicate the voltage sweep directions and correspond to the solid and dashed curves, respectively. For all measurements, BG leakage currents were  $< 10^{-5} \mu A/\mu m$ .

swing (~430 mV/dec vs. ~230 mV/dec). Fig. 3(b) shows  $I_{\rm D}$ - $V_{\text{TG}}$  curves for O<sub>2</sub>- and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> devices with  $L \approx 700$  nm. Here, the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> device shows  $I_{\rm max} \approx 260 \ \mu {\rm A}/\mu {\rm m}$  at  $V_{\text{TG}} = 20 \text{ V}$  and  $V_{\text{DS}} = 1 \text{ V}$ , on/off current ratio >10<sup>10</sup> (limited by the noise floor of the instrument), extrinsic field-effect mobility  $\mu_{\rm FE,ext} \approx 38 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  and  $V_{\rm T} = -1.6$  V. The  $\mu_{\rm FE,ext}$  and  $V_{\rm T}$  are extracted at peak transconductance. Note, at this shorter channel length, the  $V_{\rm T}$  shifts more negatively for  $O_2$ -plasma Al<sub>2</sub>O<sub>3</sub> device (-7.9 V vs. -1.6 V for  $O_3$ ), together with increased hysteresis and drain-induced barrier lowering (|DIBL|  $\approx 261 \pm 182$  mV/V for O<sub>2</sub>-plasma vs.  $128 \pm 66 \text{ mV/V}$  for O<sub>3</sub>). Such degradation may be explained by the oxygen vacancies in the channel and under the contacts, acting as dopants and defect centers, which can cause charge trapping and affect the semiconductor capacitance. However, this needs to be investigated in more detail in future studies.

Figs. 3(c,d) show output characteristics  $(I_D - V_{DS})$  for  $\sim$ 700 nm long devices with O<sub>2</sub>-plasma and O<sub>3</sub>-based Al<sub>2</sub>O<sub>3</sub> TG dielectric, respectively. The O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> device has a less negative  $V_{\rm T} \approx -3$  V vs. -10 V for O<sub>2</sub>-plasma. In addition, for the same TG overdrive voltage  $(V_{TG} - V_T = 7 \text{ V})$  at  $V_{\rm DS} = 4$  V, the drive current of the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> sample is almost double that of the O<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> device (498  $\mu$ A/ $\mu$ m vs. 266  $\mu$ A/ $\mu$ m).

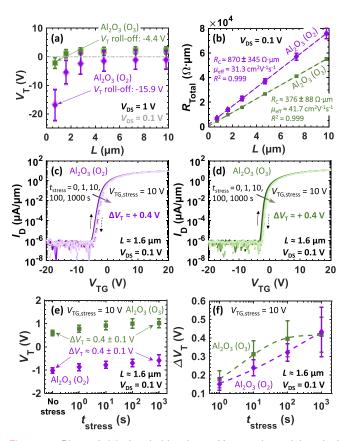

Fig. 4(a) displays  $V_{\rm T}$  roll-off *i.e.* decreasing  $V_{\rm T}$  at shorter channel lengths, ostensibly due to oxygen scavenging at the contacts [5], [11] for both O<sub>2</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> samples. The O<sub>3</sub> precursor sample shows less  $V_{\rm T}$  roll-off (-4.4 V) compared to the  $O_2$ -plasma (-15.9 V), which could be due to the passivation of a dissimilar number of oxygen vacancies in the channel during ALD. Here, the  $V_{\rm T}$  roll-off is the  $V_{\rm T}$  difference between the longest (~9.8  $\mu$ m) and shortest (~700 nm) channels. Notably,  $V_{\rm T} > 0$  V for the O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> sample down to ~1.6  $\mu$ m channel length, only becoming negative ( $V_{\rm T,avg} \approx -2.2$  V) for the shortest channel ( $\sim$ 700 nm). On the other hand, the average  $V_{\rm T}$ 's for the O<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> devices remain negative for all channel lengths. Further reduction of the dielectric and channel thickness could achieve a positive  $V_{\rm T}$  with turn-on voltage close to 0 V, at the expense of lower on-state current due to the thinner channel [12].

Fig. 4(b) shows the plot for total resistance ( $R_{\text{Total}}$ , averaged over 8 to 10 devices at each channel length) vs. channel length L for both  $O_2$  and  $O_3$ -Al<sub>2</sub>O<sub>3</sub> samples. This allows the extraction of contact resistance ( $R_{\rm C}$ ) and effective mobility ( $\mu_{\rm eff}$ ) at a given electron density,  $n \approx 2.6 \times 10^{13}$  cm<sup>-2</sup>, estimated as Authorized licensed use limited to: Stanford University. Downloaded on May 24,2023 at 18:38:47 UTC from IEEE Xplore. Restrictions apply.

Fig. 3. Top-gated (TG) transfer characteristics for (a)  $L \approx 1.6 \ \mu m$  and (b)  $L \approx 700 \ nm$ . For all measurements, TG leakage currents ( $I_{\rm G}$ ) were  $< 10^{-5} \ \mu A/\mu m$ . (c) Output characteristics ( $I_{\rm D}$ - $V_{\rm DS}$ ) for  $\sim$ 700 nm devices with O<sub>2</sub> and (d) O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> TG dielectric. Solid and dashed small arrows mark voltage sweep directions and correspond to the solid and dashed curves, respectively. Purple and green are used to denote O<sub>2</sub>-plasma and ozone (O<sub>3</sub>) Al<sub>2</sub>O<sub>3</sub> samples, respectively, in all panels.

$n = C_{\rm TG}(V_{\rm TG} - V_{\rm T})/q$ , where  $C_{\rm TG} \approx 0.28 \ \mu {\rm F/cm^2}$  for  $O_2$ -Al<sub>2</sub> $O_3$  and 0.29  $\mu$ F/cm<sup>2</sup> for  $O_3$ -Al<sub>2</sub> $O_3$  is the top-gate capacitance and q is the elementary charge. The O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> sample shows lower  $R_{\rm C} \sim 376~\Omega \cdot \mu {

m m}$  and higher  $\mu_{\text{eff}} \sim 41.7 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  compared to the O<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> sample. The difference in the  $R_{\rm C}$  and mobility values for the two samples is also present in the BG measurement before ALD capping, as evident from the lower drive current of the O2-plasma sample before ALD [Fig. 2(b)]. Before ALD capping, the samples have  $R_{\rm C}$  and  $\mu_{\rm eff}$  of ~495  $\Omega \cdot \mu m$  and ~28.6 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [Fig. 2(b)] vs.  $\sim 313 \Omega \cdot \mu m$  and  $\sim 45.2 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  [Fig. 2(c)] respectively, at  $n = 1.1 \times 10^{13}$  cm<sup>-2</sup>. This difference could be due to variation in as-deposited ITO films and/or Ni contacts, possibly caused by different chamber conditions during different runs. Notably, the  $Al_2O_3$  capping introduces further changes in these parameters, possibly due to passivation of oxygen vacancies in the ITO film during ALD.

Figs. 4(c,d) show the positive bias stress stability of  $\sim 1.6 \ \mu m \log O_2$  and  $O_3$ -Al<sub>2</sub>O<sub>3</sub> samples at a TG bias stress field of ~3.33 MV/cm. Interestingly, both samples show similar  $V_{\rm T}$  shift ( $\Delta V_{\rm T} \approx +0.4$  V) due to positive bias stress. This corresponds to a positive normalized  $V_{\rm T}$  shift of 0.12 V(MV/cm)<sup>-1</sup>, which is  $\sim 3 \times$  more stable compared to uncapped ITO devices under similar back-gate stress field reported in our prior work [13]. Figs. 4(e,f) show the evolution of  $V_{\rm T}$  and  $\Delta V_{\rm T}$  with stress time ( $t_{\rm stress}$ ) averaged across 5 devices each from O<sub>2</sub> and O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> samples. The dashed lines in Fig. 4(f) are the stretched-exponential model of  $\Delta V_{\rm T}$ time dependence [14], based on charge trapping and redistribution from the channel interface into the dielectric. The model is  $\Delta V_{\rm T} = \Delta V_{\rm T0} \{1 - \exp[-(t/\tau)^{\beta}]\}$ , where  $\Delta V_{\rm T0}$ ,  $\tau$ , and  $\beta$  represent  $\Delta V_{\rm T}$  at infinite time, the average trapping time of electrons, and a fitting exponent, respectively. In our work, these parameters are  $\sim 0.6$  V, 314 s and 0.21 for O<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub> and  $\sim 0.42$  V, 4.4 s and 0.39 for O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub>, respectively. During bias stress testing, we took DC measurements of the transfer curves, which took  $\sim 14$  s with no additional hold or delay

Fig. 4. Plots of (a) threshold voltage  $V_{\rm T}$  vs. channel length *L*, (b) total resistance  $R_{\rm Total}$  vs. *L* at electron density,  $n = 2.6 \times 10^{13}$  cm<sup>-2</sup>. Error bars represent the standard deviation among 8 to 10 devices at each channel length. Insets in (b) list the estimated contact resistance  $R_{\rm C}$  (from the vertical axis intercept of the linear fit) and the effective mobility,  $\mu_{\rm eff}$ , whereas  $R^2$  denotes the goodness of fit. (c) Positive bias stress analysis at  $V_{\rm TG, stress} = 10$  V for ~1.6  $\mu$ m devices with O<sub>2</sub> and (d) O<sub>3</sub>-Al<sub>2</sub>O<sub>3</sub> TG dielectric. Solid and dashed small arrows indicate the voltage sweep directions and correspond to the solid and dashed curves, respectively. Evolution of (e)  $V_{\rm T}$  and (f)  $V_{\rm T}$  shift,  $\Delta V_{\rm T}$ , vs. stress time,  $t_{\rm stress}$  for  $V_{\rm TG, stress} = 10$  V. Error bars in (e, f) mark the variability among 5 devices. Dashed lines in (f) are fit to the stretched-exponential model in [14]. Purple and green are used to denote O<sub>2</sub>-plasma and ozone (O<sub>3</sub>) Al<sub>2</sub>O<sub>3</sub> samples, respectively, in all panels.

time in between the stress and measurement. The stress time was accumulated over all cycles.

# **IV. CONCLUSION**

We report top-gated ITO transistors with good  $R_{\rm C} \sim 376 \ \Omega \cdot \mu \text{m}$  and  $\mu_{\rm eff} \sim 42 \ \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ . We achieve  $I_{\rm max} \approx 260 \ \mu \text{A}/\mu \text{m}$  at  $V_{\rm DS} = 1 \ \text{V}$  in a  $\sim 700 \ \text{nm}$  long channel with O<sub>3</sub>-based Al<sub>2</sub>O<sub>3</sub> as the top dielectric. We show that, both O<sub>3</sub> and O<sub>2</sub>-plasma precursors during the ALD of the top-gate dielectric produce bias stress stable devices. Using O<sub>3</sub> precursor over O<sub>2</sub>-plasma demonstrates the advantage for minimizing the  $V_{\rm T}$  roll-off after ALD as well as reducing short channel effects. These results are important for ITO channel transistor applications in BEOL and 3D integration. They also open a pathway towards enhancing oxide transistor performance by channel length scaling and improved gate control, *i.e.* dual-gating or gate-all-around structures.

#### ACKNOWLEDGMENT

The authors acknowledge the ozone generator provided by TMEIC Corporation. They also thank Profs. Krishna Saraswat and Rebecca L. Peterson for helpful discussions.

Authorized licensed use limited to: Stanford University. Downloaded on May 24,2023 at 18:38:47 UTC from IEEE Xplore. Restrictions apply.

#### REFERENCES

- [1] C. Fenouillet-Beranger, L. Brunet, P. Batude, L. Brevard, X. Garros, M. Casse, J. Lacord, B. Sklenard, P. Acosta-Alba, S. Kerdiles, A. Tavernier, C. Vizioz, P. Besson, R. Gassilloud, J.-M. Pedini, J. Kanyandekwe, F. Mazen, A. Magalhaes-Lucas, C. Cavalcante, D. Bosch, M. Ribotta, V. Lapras, M. Vinet, F. Andrieu, and J. Arcamone, "A review of low temperature process modules leading up to the first (≤500 °C) planar FDSOI CMOS devices for 3-D sequential integration," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3142–3148, Jul. 2021, doi: 10.1109/TED.2021.3084916.

- [2] M. Si, A. Murray, Z. Lin, J. Andler, J. Li, J. Noh, S. Alajlouni, C. Niu, X. Lyu, D. Zheng, K. Maize, A. Shakouri, S. Datta, R. Agrawal, and P. D. Ye, "BEOL compatible indium-tin-oxide transistors: Switching of ultrahigh-density 2-D electron gas over 0.8 × 10<sup>14</sup>/cm<sup>2</sup> at oxide/oxide interface by the change of ferroelectric polarization," *IEEE Trans. Electron Devices*, vol. 68, no. 7, pp. 3195–3199, Jul. 2021, doi: 10.1109/TED.2021.3061038.

- [3] S. Li, M. Tian, C. Gu, R. Wang, M. Wang, X. Xiong, X. Li, R. Huang, and Y. Wu, "BEOL compatible 15-nm channel length ultrathin indiumtin-oxide transistors with  $I_{on} = 970 \ \mu A/\mu m$  and on/off ratio near  $10^{11}$ at  $V_{ds} = 0.5$  V," in *IEDM Tech. Dig.*, Dec. 2019, pp. 3.5.1–3.5.4, doi: 10.1109/IEDM19573.2019.8993488.

- [4] M. Si, Z. Lin, Z. Chen, X. Sun, H. Wang, and P. D. Ye, "Scaled indium oxide transistors fabricated using atomic layer deposition," *Nature Electron.*, vol. 5, no. 3, pp. 164–170, Feb. 2022, doi: 10.1038/s41928-022-00718-w.

- [5] S. Subhechha, N. Rassoul, A. Belmonte, R. Delhougne, K. Banerjee, G. L. Donadio, H. Dekkers, M. J. van Setten, H. Puliyalil, M. Mao, S. Kundu, M. Pak, L. Teugels, D. Tsvetanova, N. Bazzazian, L. Klijs, H. Hody, A. Chasin, J. Heijlen, L. Goux, and G. S. Kar, "First demonstration of sub-12 nm Lg gate last IGZO-TFTs with oxygen tunnel architecture for front gate devices," in *Proc. Symp. VLSI Technol.*, 2021, pp. 1–2.

- [6] S. Li, M. Tian, Q. Gao, M. Wang, T. Li, Q. Hu, X. Li, and Y. Wu, "Nanometre-thin indium tin oxide for advanced high-performance electronics," *Nature Mater.*, vol. 18, no. 10, pp. 1091–1097, 2019, doi: 10.1038/s41563-019-0455-8.

- [7] M. Si, J. Andler, X. Lyu, C. Niu, S. Datta, R. Agrawal, and P. D. Ye, "Indium-tin-oxide transistors with one nanometer thick channel and ferroelectric gating," ACS Nano, vol. 14, no. 9, pp. 11542–11547, Sep. 2020, doi: 10.1021/acsnano. 0c03978.

- [8] S. Li, C. Gu, X. Li, R. Huang, and Y. Wu, "10-nm channel length indium-tin-oxide transistors with  $I_{on} = 1860 \ \mu A/\mu m$ ,  $G_m = 1050 \ \mu S/\mu m$  at  $V_{ds} = 1$  V with BEOL compatibility," in *IEDM Tech. Dig.*, Dec. 2020, pp. 40.5.1–40.5.4, doi: 10.1109/IEDM13553.2020.9371966.

- [9] C. R. Allemang and R. L. Peterson, "Passivation of thin channel zinc tin oxide TFTs using Al<sub>2</sub>O<sub>3</sub> deposited by O<sub>3</sub>-based atomic layer deposition," *IEEE Electron Device Lett.*, vol. 40, no. 7, pp. 1120–1123, Jul. 2019, doi: 10.1109/LED.2019.2914238.

- [10] K. Han, Q. Kong, Y. Kang, C. Sun, C. Wang, J. Zhang, H. Xu, S. Samanta, J. Zhou, H. Wang, A. V.-Y. Thean, and X. Gong, "Indium-gallium-zinc-oxide (IGZO) nanowire transistors," *IEEE Trans. Electron Devices*, vol. 68, no. 12, pp. 6610–6616, Dec. 2021, doi: 10.1109/TED.2021.3113893.

- [11] D. H. Kang, J. U. Han, M. Mativenga, S. H. Ha, and J. Jang, "Threshold voltage dependence on channel length in amorphousindium-gallium-zinc-oxide thin-film transistors," *Appl. Phys. Lett.*, vol. 102, no. 8, Feb. 2013, Art. no. 083508, doi: 10.1063/ 1.4793996.

- [12] A. Charnas, Z. Lin, Z. Zhang, and P. D. Ye, "Atomically thin  $In_2O_3$  field-effect transistors with  $10^{17}$  current on/off ratio," *Appl. Phys. Lett.*, vol. 119, no. 26, Dec. 2021, Art. no. 263503, doi: 10.1063/5.0075166.

- [13] L. Hoang, A. Daus, S. Wahid, J. Kwon, J.-S. Ko, S. Qin, M. Islam, K. C. Saraswat, H.-S.-P. Wong, and E. Pop, "Bias stress stability of ITO transistors and its dependence on dielectric properties," in *Proc. Device Res. Conf. (DRC)*, Jun. 2022, pp. 1–2, doi: 10.1109/DRC55272.2022. 9855789.

- [14] J.-M. Lee, I.-T. Cho, J.-H. Lee, and H.-I. Kwon, "Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors," *Appl. Phys. Lett.*, vol. 93, no. 9, 2008, Art. no. 093504, doi: 10.1063/1.2977865.