# Fringe current correction for unpatterned-channel thin-film transistors including contact resistance and velocity saturation effects

Cite as: J. Appl. Phys. 137, 224504 (2025); doi: 10.1063/5.0266349

Submitted: 18 February 2025 · Accepted: 19 March 2025 ·

Published Online: 13 June 2025

View Online

Export Citation

CrossMark

Çağıl Köroğlu,<sup>1</sup> Alwin Daus,<sup>2</sup> Sumaiya Wahid,<sup>1</sup> Miguel Muñoz Rojo,<sup>3</sup> and Eric Pop<sup>1,4,5,a</sup>

## AFFILIATIONS

<sup>1</sup> Department of Electrical Engineering, Stanford University, Stanford, California 94305, USA

<sup>2</sup> Institute of Semiconductor Engineering, University of Stuttgart, Stuttgart 70569, Germany

<sup>3</sup> 2D Foundry, Instituto de Ciencia de Materiales de Madrid (ICMM), CSIC, Madrid 28049, Spain

<sup>4</sup> Department of Materials Science & Engineering, Stanford University, Stanford, California 94305, USA

<sup>5</sup> Department of Applied Physics, Stanford University, Stanford, California 94305, USA

<sup>a</sup>Author to whom correspondence should be addressed: [epop@stanford.edu](mailto:epop@stanford.edu)

## ABSTRACT

Thin-film transistors (TFTs), e.g., based on organic semiconductors, oxides, perovskites, and two-dimensional materials (such as graphene or MoS<sub>2</sub>), are often fabricated without patterning a rectangular channel strip between the contacts, to keep the fabrication flow simple and the material pristine. However, this makes it difficult to extract current density and mobility due to fringing currents, which, if ignored, lead to overestimation of these device metrics. Furthermore, the extent of current spreading varies wildly from device to device depending on geometry, bias, as well as transport characteristics such as contact resistance and velocity saturation. We explore the impact of each of these factors through detailed simulations and discuss the subtle ways in which bias-dependent fringe currents can impact device characteristics. For TFTs where contact resistance and velocity saturation are negligible, we provide a simple analytical model that quantifies fringe currents with an error of  $\leq 0.01\%$  in common geometries. For unpatterned-channel TFTs with significant contact resistance or velocity saturation, our simulations reveal that either effect can more than double the fringe current. This can translate to the overestimation of current density and mobility by over 70%, even in devices with a contact width over 10 $\times$  the channel length. If patterning the channel and using very wide contacts are impractical, proper device characterization thus necessitates correcting for fringe currents. By highlighting the utility of simulations and analytical models in this endeavor, this work provides insights into greatly assisting the rapid quantitative assessment of TFTs and intuition for identifying the intricate effects of current spreading on device characteristics.

13 June 2025 19:18:45

© 2025 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 4.0 International (CC BY-NC-ND) license (<https://creativecommons.org/licenses/by-nc-nd/4.0/>). <https://doi.org/10.1063/5.0266349>

## I. INTRODUCTION

In the course of research on new materials for transistors, it is not uncommon to do field-effect measurements on test structures that comprise an extremely simple process flow. A typical experimental approach would start with a highly doped Si substrate with thermally grown SiO<sub>2</sub> used for back-gating. Onto this substrate, the thin-film semiconductor under investigation is deposited, followed by the formation of electrical contacts by, e.g., shadow evaporation or lithographic patterning of metals. Often an important step is left out, which is the patterning of the semiconductor channel to

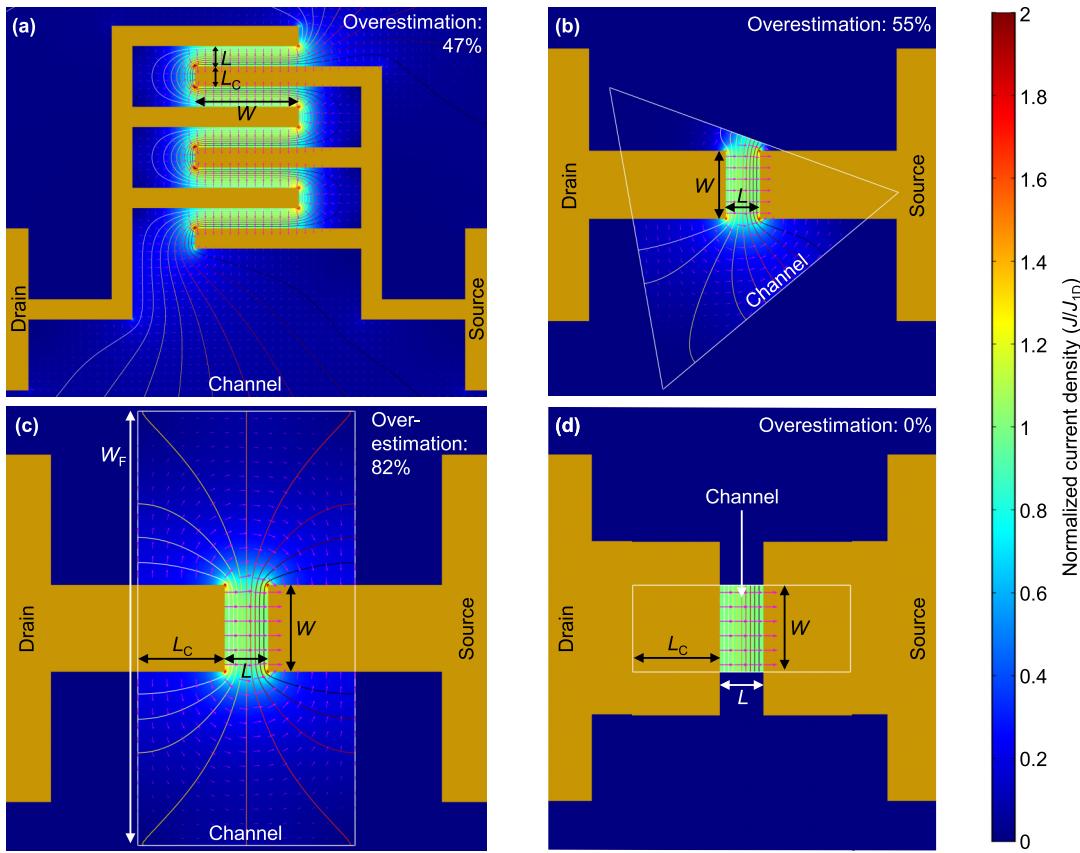

accurately define the path of current flow and confine it to one direction. Reasons for this can be manifold, like the unavailability of mature lithography or etch processes, environmental or solvent instability of the material under investigation, or avoiding damage to the channel (e.g., by introducing defects or edge roughness) during processing. Such an approach is especially common in organic/polymer,<sup>1,2</sup> oxide,<sup>3–5</sup> perovskite,<sup>6–11</sup> graphene,<sup>12–16</sup> black phosphorus,<sup>17–21</sup> and other two-dimensional (2D) material<sup>22–29</sup> research, e.g., for 2D transistors fabricated on mechanically exfoliated material flakes. Figures 1(a) and 1(b) show simulated

13 June 2025 19:18:45

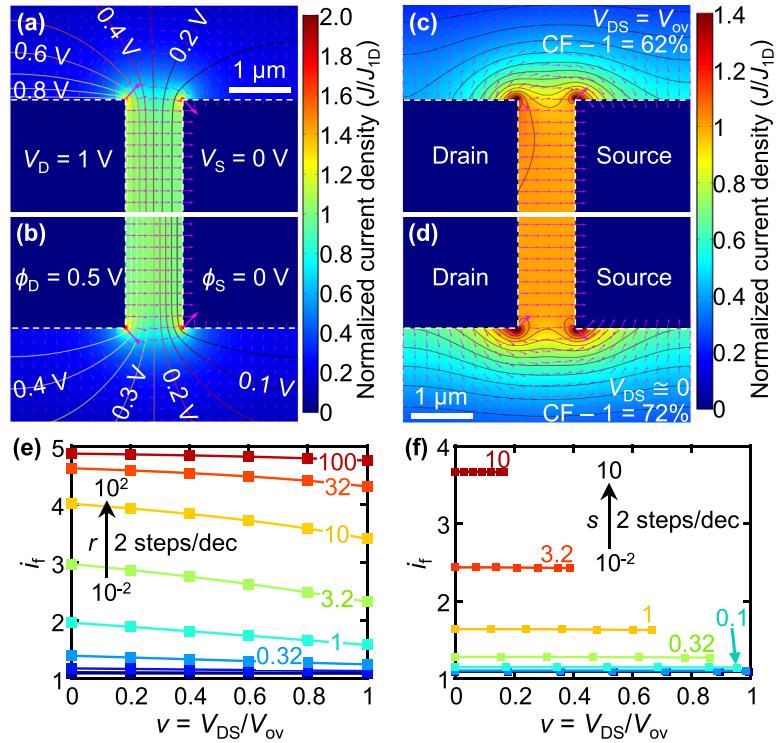

**FIG. 1.** Lateral current density distribution in several thin-film transistors (TFTs) in linear region, with negligible contact resistance and velocity saturation. Colors represent the current density  $J$ , normalized by the current density  $J_{1D}$  of a patterned-channel TFT with the same contact spacing (color bar to the right of the figure). Arrows indicate the current density direction. The colored lines are equipotential curves. The gated channel area is delineated by a white line (the gate is not shown and could be above or below the channel). (a) An interdigitated unpatterned-channel TFT where the entire device area overlaps with the gate electrode, usually a global back gate in the form of a conductive substrate. This geometry is common in devices with a solution-processed channel. Not accounting for fringe currents overestimates the current density by 47%. (b) Current distribution in an unpatterned TFT with an irregularly shaped channel. This kind of geometry is especially common in 2D material research. Neglecting fringe currents overestimates the current density by 55%. (c) Current distribution in a TFT with the channel wider than the contacts. In addition to unpatterned-channel TFTs that sometimes have such geometry, the channel can be intentionally patterned this way to improve high-frequency performance. Neglecting fringe currents causes a current density overestimation of 82%. (d) Current density  $J_{1D}$  in a patterned-channel TFT, with channel width less than contact width.

current densities in typical examples of devices of this kind frequently found in the literature. Another type of transistor is sometimes encountered where the channel is intentionally patterned wider than the contacts—as depicted in Fig. 1(c)—to obtain higher currents and improve high-frequency performance, for instance.<sup>30,31</sup>

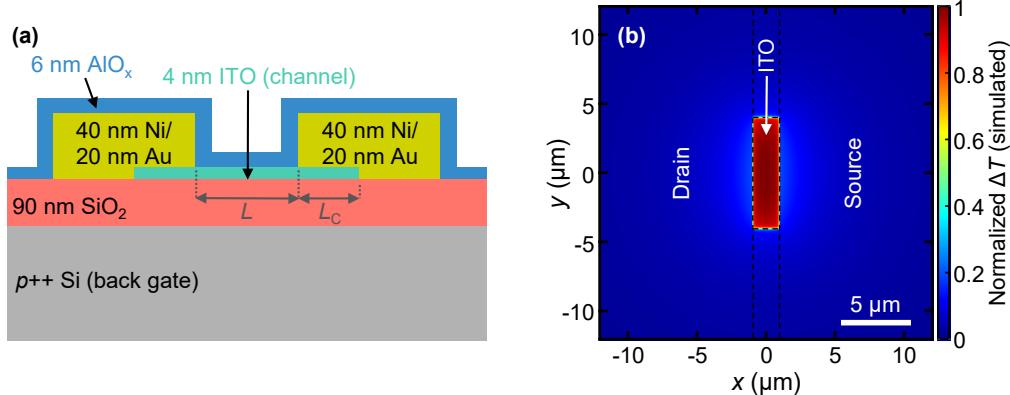

However, none of these device types have a well-defined rectangular strip of channel with uniform current density, like in Fig. 1(d). Instead, the channel is often wider than the source and drain contact electrodes, causing fringe currents to flow between them and precluding straightforward extraction of the current density or mobility, which are crucial performance metrics. Fringe currents have been visualized experimentally by measuring the potential<sup>32</sup> or temperature<sup>30</sup> distribution across devices. Using the latter

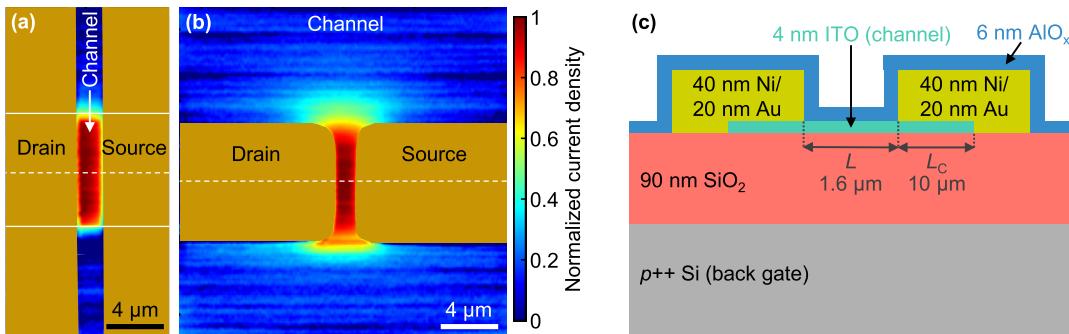

approach, we have mapped the current density distribution in patterned and unpatterned indium tin oxide (ITO) transistors,<sup>33</sup> as shown in Figs. 2(a) and 2(b), respectively. It can be seen that the unpatterned device has current flowing in an area wider than the contact width. The details of the devices, self-heating measurements, and data processing are provided in Sec. S1 in the supplementary material.

In studies that feature unpatterned-channel thin-film transistors (TFTs), often only the total drain current is reported, without estimating the width-normalized current density, which is an important quantity for comparing different transistors or for extracting intrinsic parameters such as mobility. Current density in unpatterned-channel TFTs is sometimes extracted by simply dividing the current by the contact width, thus neglecting the

**FIG. 2.** Current density maps extracted from thermal measurements on (a) a patterned and (b) an unpatterned-channel indium tin oxide (ITO) transistor. Solid white lines delineate the patterned channel in (a). Fringe currents can be clearly seen in the unpatterned device. First, the self-heating induced temperature rise of each device is mapped via scanning thermal microscopy.<sup>34–37</sup> Current density is then extracted by using the fact that the temperature rise at each point is approximately proportional to the square of the local current density. (c) Cross section of the measured device geometry, along the direction marked with dashed lines in panels (a) and (b).

fringe currents. This causes the current density, mobility, and transconductance to be substantially overestimated in many cases, by an amount depending on the device geometry as well as other parameters to be discussed in this work.

Okamura *et al.*<sup>38</sup> previously noted that studies using unpatterned-channel TFTs reported much higher mobilities than those with patterned channels, and argued using experiments and simulations that the former were overestimated due to fringe currents. Dipu Kabir *et al.*<sup>39</sup> described a model that can estimate the fringe current flow in unpatterned-channel organic TFTs with approximations obtained by conformal mapping techniques. However, the calculations require values that are numerically pre-computed and/or stored in a look-up table. Chen *et al.*<sup>32</sup> examined fringe currents in IGZO and *a*-Si:H TFTs of various geometries, visualizing the potential variation using scanning Kelvin probe microscopy. They observed that fringe currents are nearly independent of bias voltages in the linear and saturation regimes, but did not provide further insights or discussions on the matter. Pei *et al.*<sup>2</sup> studied fringe current contributions in organic TFTs starting with unpatterned devices, and later patterning the channel by scratching it with a probe tip. They measured slightly lower fringe currents in the saturation regime, attributing them to the electric field distribution during pinch-off, an assumption we revisit in this study. Daus *et al.*<sup>22</sup> fabricated monolayer MoS<sub>2</sub> TFTs on flexible substrates, and used simulations to extract width-normalized currents, accounting for the effect of device geometry and contact resistance on current spreading. The way contact resistance ( $R_C$ ) and velocity saturation (VS) impact fringe currents is generally absent in the literature (except in Daus *et al.*,<sup>22</sup> where  $R_C$  is considered), despite the fact that these effects are typically prominent in short-channel devices. In addition, although the role of the device bias point on current spreading has been noted to be minor or negligible,<sup>2,32</sup> deeper insights into this effect are lacking.

In the present work, motivated by our recent experimental study,<sup>22</sup> we formulate the problem of fringe currents in unpatterned TFTs in terms of a minimal set of parameters that quantify the device geometry, bias, and transport properties (including  $R_C$ ,

contact transfer length, and VS), and then explore the effect of each of these aspects on a correction factor (CF) that accounts for fringe currents. For devices where  $R_C$  and VS are negligible, we provide a simple analytical expression to account for the fringe currents, without requiring look-up tables or numerical iteration.

## II. METHODS

Consider an *n*-channel TFT with an unpatterned-channel whose top view is given in Fig. 1(c). We may express the current through it as

$$I = WJ_{ID} + 2I_f, \quad (1)$$

where  $W$  is the contact width and  $J_{ID}$  is the current per unit width (i.e., current density). Here, the first term corresponds to the current of an identical TFT patterned with a channel width of  $W$  where current flow is “one-dimensional” (1D), while the second term is the contribution from the fringe current  $I_f$  that flows on either side of the channel (hence the factor of 2). We may also write Eq. (1) as

$$I = CF \times WJ_{ID}, \quad (2)$$

where we have introduced a *correction factor*  $CF = 1 + 2I_f/(WJ_{ID}) \geq 1$  as the ratio of the unpatterned-channel TFT current to that it would have with a properly defined channel. In practice,  $I$  is typically measured directly with the goal of estimating  $J_{ID}$ : the performance metric that is directly linked to device parameters of interest, such as  $R_C$  and the channel carrier mobility  $\mu_n$ . If one can predict CF, one can estimate  $J_{ID}$ .<sup>22</sup> On the other hand, because  $J_{ID} = I/(CF \cdot W)$ , assuming  $CF = 1$  and neglecting current spreading can significantly overestimate  $J_{ID}$  and result in serious material or device mischaracterization. To aid in the extraction of  $J_{ID}$ , the focus of this study is to model the impacts of various device parameters on CF.

Both  $J_{ID}$  and CF are functions of a set of device, material, and bias parameters,  $\{p_i\}$ , some of which may be unknown, such as  $\mu_n$ ,  $R_C$ , and saturation velocity. Even if one knows the functions  $J_{ID}(\{p_i\})$

13 June 2025 19:18:45

and  $CF(\{p_i\})$  precisely, the total current is proportional to their product [see Eq. (2)], and different sets of  $\{p_i\}$  can yield the same total current. In other words, measuring  $I$  is generally not enough to uniquely and exactly determine  $\{p_i\}$  and, hence,  $J_{1D}$  and  $CF$ . For example, a high  $\mu_n$  and high  $R_C$  can yield the same device current as a low  $\mu_n$  and low  $R_C$ .<sup>22</sup> Still, if one knows the total current  $I$  and the function  $CF(\{p_i\})$ , with reasonable bounds on the unknown parameters  $\{p_i\}$ , one can determine  $\{p_i\}$  and  $J_{1D}$  with acceptable uncertainty, without neglecting the effects of fringe currents. This approach is illustrated in our previous experimental work,<sup>22</sup> which we revisit in Sec. S2 in the [supplementary material](#) and expand upon in the framework of the present paper. Therefore, precise determination of  $CF(\{p_i\})$  is important for accurate characterization of unpatterned-channel TFTs, and is the goal of this work.

Suppose for the time being that the unpatterned-channel TFT is otherwise ideal (i.e., with negligible  $R_C$  and  $VS$ ) and deep in the linear region, i.e.,  $V_{ov} \gg V_{DS}$ , where  $V_{ov} = V_{GS} - V_T$  is the overdrive voltage,  $V_{DS}$  is the drain-source voltage,  $V_{GS}$  is the gate-source voltage, and  $V_T$  is the threshold voltage for an  $n$ -channel device. The channel then has a nearly uniform sheet conductance  $G_{sh} = \mu_n C_{ox} V_{ov}$ , where  $C_{ox}$  is the gate insulator capacitance per unit area, and we may write the patterned-channel device current as

$$WJ_{1D} = G_{sh} V_{DS} \frac{W}{L}. \quad (3)$$

In order to eliminate the trivial dependence of  $I_f$  on channel conductance and bias, we introduce a *normalized* fringe current  $i_f = I_f / (G_{sh} V_{DS})$  such that

$$I = WJ_{1D} + 2I_f = G_{sh} V_{DS} \frac{W}{L} \left( 1 + 2 \frac{i_f}{W/L} \right). \quad (4)$$

In general, dropping the requirements that  $V_{DS}$  be small and  $R_C$  and  $VS$  be negligible, we may write

$$I = \left( 1 + 2 \frac{i_f}{W/L} \right) WJ_{1D}, \quad (5)$$

where  $J_{1D}$  is the current per unit width of a transistor with a patterned channel such as that in [Fig. 1\(d\)](#), and the *normalized* fringe current is defined generally as  $i_f = I_f / (LJ_{1D})$ . We note that  $J_{1D} = G_{sh} V_{DS} / L$  when  $R_C$  and  $VS$  can be neglected and  $V_{DS} \ll V_{ov}$  [i.e., in Eq. (3)], but its general form is more complex and will be discussed below. Comparing Eq. (5) with Eq. (2), we see that  $CF$  and  $i_f$  are directly related through

$$CF = 1 + 2 \frac{i_f}{W/L}. \quad (6)$$

$CF$  is easy to interpret as the factor by which the current in an unpatterned TFT exceeds that in a patterned-channel TFT and, hence, the factor by which current density and mobility are overestimated if current spreading is not accounted for. However, we shall see in Sec. III A that  $i_f$  is almost independent of  $W$  and  $L$  in many cases, so it is a more convenient parameter than  $CF$  for quantifying current spreading.

At high electric fields, rather than increasing linearly with the field, electron (or hole) drift velocity approaches a constant saturation velocity  $v_{sat}$  which in crystalline semiconductors is caused primarily by hot carriers losing energy to optical phonons.<sup>40</sup> To model field-dependent drift velocity, we adopt the simple Caughey-Thomas VS model<sup>41</sup> with parameter  $\beta = 1$ , in which the low-field electron mobility  $\mu_n$  along the channel is locally reduced by a factor of  $[1 + (|E|/E_c)^\beta]^{1/\beta}$ , where  $E$  is the lateral electric field and  $E_c = v_{sat}/\mu_n$  is the critical field.<sup>42,43</sup> This model has been applied—sometimes with different values of parameter  $\beta$ —to crystalline<sup>44,45</sup> and amorphous<sup>46</sup> Si, transition metal dichalcogenides,<sup>47</sup> graphene,<sup>48</sup> and amorphous oxides<sup>49</sup> (with modification to account for trapped charge carriers). VS with field-dependent velocity similar to that given by the Caughey-Thomas model has also been observed in organic semiconductors and attributed to either optical phonon emission by hot carriers or band non-parabolicity.<sup>50,51</sup>

To model contact resistance, we assume that both the drain and source contacts are characterized by the same specific contact resistivity  $\rho_C$ , and that the sheet conductance of the semiconductor overlapping with contact electrodes is  $G_{sh,C}$  (in general, this will be different from the sheet conductance in the channel due to the electrostatic influence of the contact metal, or due to defects introduced by metal deposition). We also use the well-known results of the transmission line model for contact resistance<sup>52-54</sup> to write  $G_{sh,C}$  and  $\rho_C$  in terms of contact resistance (per unit contact width)  $R_C$  and transfer length  $L_T$ , quantities that are typically easier to measure using, e.g., transfer length method test structures:

$$\begin{aligned} \rho_C &= \frac{R_C L_T}{\coth \frac{L_C}{L_T}}, \\ G_{sh,C} &= \frac{L_T}{R_C} \coth \frac{L_C}{L_T}. \end{aligned} \quad (7)$$

For purely one-dimensional (1D) charge transport (as in a patterned channel), in the standard gradual channel approximation with drift current, the width-normalized drain current in the linear (triode) regime is given by<sup>43</sup>

$$J_{1D} = \frac{\mu_n C_{ox}}{1 + \frac{V'_{DS}}{LE_c}} \frac{1}{L} \left( V'_{ov} V'_{DS} - \frac{V'^2_{DS}}{2} \right), \quad (8)$$

where  $V'_{DS} = V_{DS} - 2R_C J_{1D}$  and  $V'_{ov} = V_{ov} - R_C J_{1D}$ , the drain-source and overdrive voltages are reduced by the series voltage drops in the contacts due to  $R_C$  (within the assumption that source and drain contact resistances are both  $R_C$ ). Saturation current can be obtained as the maximum value attained by the expression in Eq. (8) as  $V_{DS}$  is varied. The closed-form solution to Eq. (8) as well as expressions for the saturation current  $J_{1D,sat}$  and voltage  $V_{DS,sat}$  are provided in Sec. S3 in the [supplementary material](#). The dependence of  $CF$  and  $i_f$  on mechanisms causing the current to increase beyond  $J_{1D,sat}$  as  $V_{DS}$  is increased past  $V_{DS,sat}$  (e.g., channel length modulation and drain-induced barrier lowering) is not investigated in this study. In general, exact closed-form solutions are not available for a TFT with an unpatterned-channel and lateral current

13 June 2025 19:18:45

spreading, necessitating numerical solutions. In this work, we use the finite-element method (FEM) to simulate transport in such unpatterned-channel TFTs: the mathematical formulation of the general problem solved numerically is described in detail in Sec. S4 in the [supplementary material](#).

A TFT has many parameters describing its geometry ( $W$ ,  $L$ ,  $L_C$ ), transport properties ( $\mu_n$ ,  $C_{ox}$ ,  $v_{sat}$ ,  $R_C$ ,  $L_T$ ), and bias voltages ( $V_{ov}$ ,  $V_{DS}$ ): all of these influence the fringe current, some of them in ways that are tightly connected. To study the dependence of current spreading on geometry, transport, and bias while keeping the number of variables manageable, we prove in Sec. S5 in the [supplementary material](#) that these parameters can be decoupled and distilled down to six dimensionless parameters listed in [Table I](#) on which the CF and  $i_f$  depend exclusively.

$w = W/L$  is the aspect ratio of the strip of the channel that lies between the contacts.  $\ell_C = L_C/L$  quantifies the length of the contact metal overlap with the channel.  $\ell_T = L_T/L$  quantifies the contact transfer length.  $r$  is the ratio of  $R_C$  to the channel resistance for a patterned-channel TFT at  $V_{DS} \approx 0$ , and thus quantifies how contact dominated the device is.  $s$  quantifies the current degradation due to VS: note that the effective mobility of a patterned-channel TFT with  $R_C = 0$  is  $\mu_n/(1+s)$  [see Eq. (8)]. Finally,  $v = V_{DS}/V_{ov}$  determines the device's bias point, specifically how close the channel is to pinch-off. For negligible  $R_C$  ( $r \geq 0$ ) and VS ( $s \geq 0$ ), the device is in the linear regime for  $v < 1$  and reaches saturation (i.e., pinch-off) at  $v = 1$ . Increasing  $R_C$  (and, hence,  $r$ ) increases the value of  $v$  at which the device reaches saturation, and decreasing  $E_c$  (increasing  $s$ ) has the opposite effect.

To keep the problem space manageable, we restrict the quantitative results in this work to the unpatterned device geometry in [Fig. 1\(c\)](#) with the total semiconductor film width  $W_F$  that is large enough not to affect the current distribution.  $W_F$  can be considered large enough if  $W_F \gtrsim W + 2L_C$ , and if this is not the case, an additional parameter such as  $w_F = W_F/L$  could be added to those in [Table I](#). We note that the parameters in [Table I](#) may be implicitly connected or may depend on additional parameters. For example,  $r$  might have an additional implicit dependence on  $V_{ov}$  due to bias-dependent mobility or might depend on the channel material and thickness through their influence on effective  $C_{ox}$ . The current spreading analysis should take these dependencies into account by using the correct set of parameters for the device and the bias point at hand. If these dependencies are not known *a priori*, as is often the case in practice, one may assign physically sensible bounds to unknown parameters, which will translate to a (hopefully acceptable) uncertainty in the estimated  $J_{1D}$  and CF. This approach is illustrated in Sec. S2 in the [supplementary material](#).

### III. RESULTS AND DISCUSSION

#### A. Current spreading for ideal transport

In this section, we analyze the case where transport in the channel is “ideal” in the sense that  $R_C$  and VS are both negligible. This is often a good approximation for long-channel ( $\gtrsim 1 \mu\text{m}$ ) transistors at moderate  $V_{DS}$  and will also establish a reference with which “non-ideal” devices can be compared. To study how the normalized fringe current  $i_f$ , and hence CF, are influenced by geometry alone, we also restrict the discussion in this section to  $V_{DS} \ll V_{ov}$ ,

**TABLE I.** The six dimensionless parameters that affect current spreading in unpatterned-channel TFTs.

| Parameter                                             | Significance                                                                                                                                                                                                                                                 |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $w = W/L$                                             | Channel aspect ratio                                                                                                                                                                                                                                         |

| $\ell_C = L_C/L$                                      | Normalized contact length (length of overlap of contact electrode and channel)                                                                                                                                                                               |

| $\ell_T = L_T/L$                                      | Normalized contact transfer length. $\ell_C \gg \ell_T$ means electrically long (or “edge”) contacts, $\ell_C \ll \ell_T$ means electrically short contacts.                                                                                                 |

| $r = G_{sh}^0 R_C/L$<br>$= \mu_n C_{ox} V_{ov} R_C/L$ | 1D contact resistance, normalized by 1D channel resistance. Quantifies how contact dominated the device current is. Here, $G_{sh}^0 = \mu_n C_{ox} V_{ov}$ is the semiconductor sheet conductance for $V_{DS} \ll V_{ov}$ , i.e., deep in the linear regime. |

| $s = V_{DS}/(LE_c)$                                   | Velocity saturation parameter. 1D current degradation term due to VS. Ratio of the average lateral field to the critical field. Quantifies how VS limited the device current is.                                                                             |

| $v = V_{DS}/V_{ov}$                                   | Bias parameter. Quantifies how close the device is to pinch-off (saturation).                                                                                                                                                                                |

although this restriction will be shown to be unnecessary in Sec. III D. Under these conditions, the differential equation for channel potential [Eq. (S8) in the [supplementary material](#)] reduces to Laplace’s equation, with constant potential (Dirichlet) boundary conditions at the contacts.

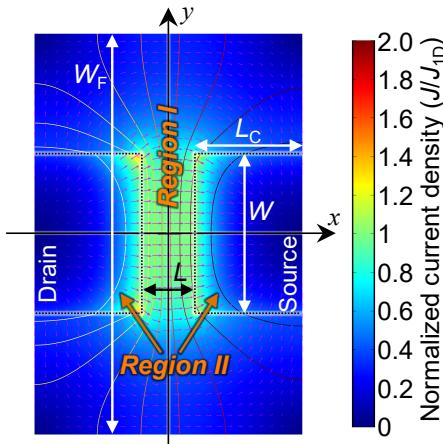

Conformal mapping techniques (the Schwarz–Christoffel transformation in particular)<sup>55</sup> have long been used to solve Laplace’s equation on relatively complex geometries for applications in electrostatics,<sup>56–58</sup> heat transfer,<sup>59,60</sup> fluid mechanics,<sup>61</sup> and more.<sup>62</sup> With a suitable conformal map, it is possible to obtain an exact analytical expression for  $i_f$  in the case of infinitely wide contacts ( $w = W/L \rightarrow \infty$ ):

$$i_{f,ideal} = \frac{1}{\pi} [(1 + \ell_C) \log(1 + \ell_C) - \ell_C \log \ell_C + \log 2], \quad (9)$$

where  $\ell_C = L_C/L$ , and the corresponding  $CF_{ideal}$  is calculated via Eq. (6). A derivation is provided in Sec. S6 in the [supplementary material](#). Equation (9) has previously been reported (without derivation) to arise from the solution to a mathematically equivalent boundary value problem<sup>63</sup> and is also applicable to the calculation of the fringe capacitance per unit length of a symmetric strip transmission line of infinite width.<sup>64</sup>

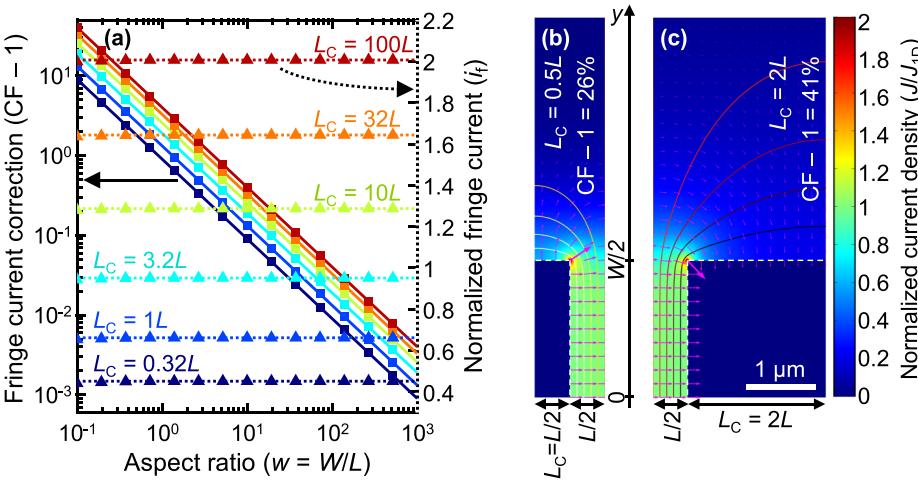

Remarkably, while the normalized fringe current given by Eq. (9) is only strictly valid for aspect ratio  $w \rightarrow \infty$ ,  $i_f$  turns out to be almost independent of  $w$  for all but very small  $w$ , as shown in [Fig. 3\(a\)](#). With  $L_C > 0.3L$ ,  $i_f$  deviates from  $i_{f,ideal}$  by  $< 3\%$  for  $0.1 \leq w \leq 1$ , and only by  $< 0.01\%$  for  $w \geq 1$  (with even better agreement for higher  $L_C$ ), so Eq. (9) is an excellent approximation for the typical unpatterned-channel transistors where  $R_C$  and VS are

13 June 2025 19:18:45

negligible. As such, it establishes a useful baseline to which the CF and  $i_f$  results for devices with non-zero transport ( $\ell_T$ ,  $r$ ,  $s$ ) and bias ( $v$ ) parameters can be compared.

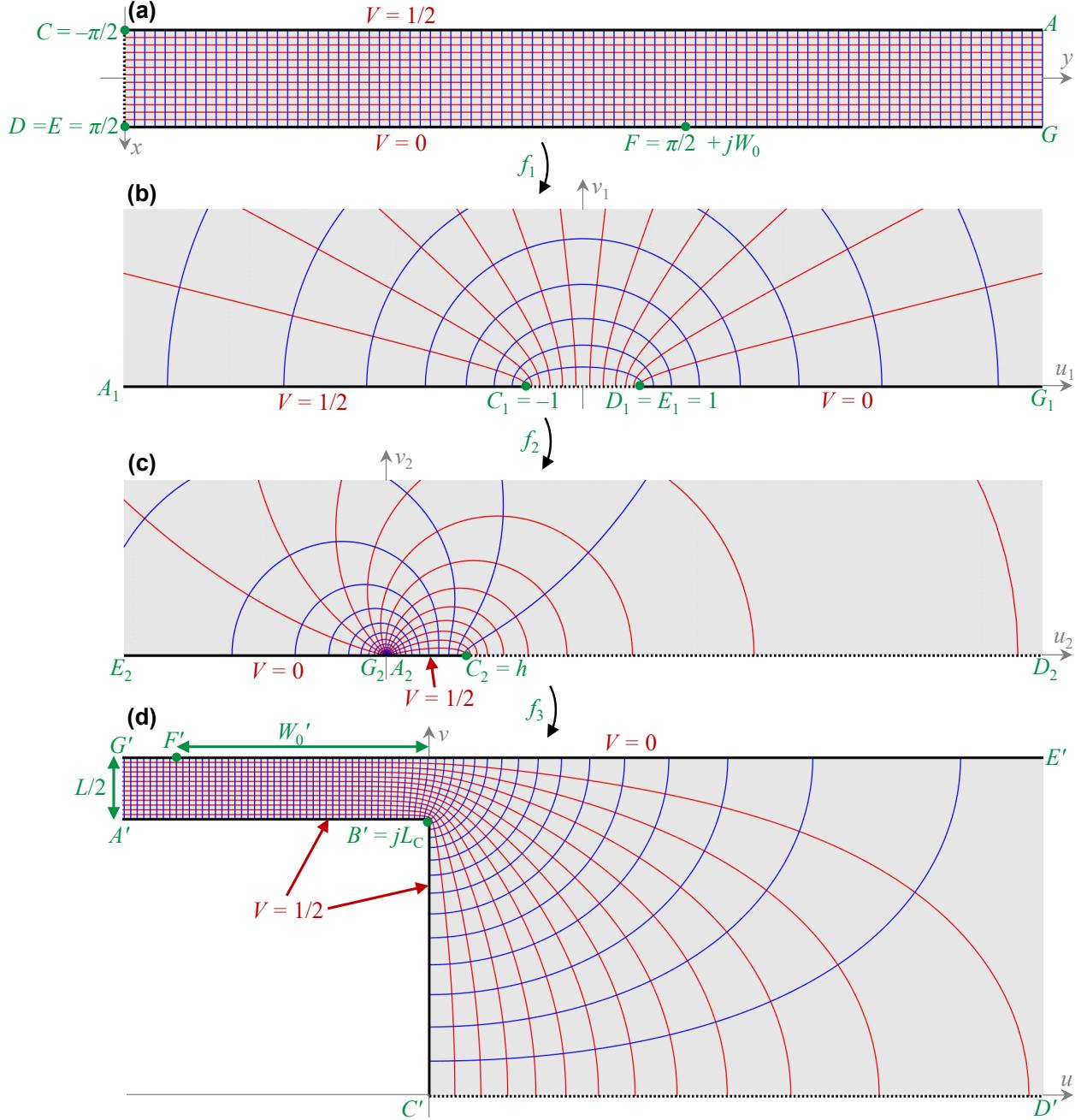

Figure 3(a) also indicates that current spreading increases with  $L_C$ . This can be better understood by comparing Figs. 3(b) and 3(c): the current density distribution extends further along the  $y$  direction in the device with longer contacts. It is shown in Sec. S7 in the *supplementary material* that outside the strip of the channel between the contacts, current density drops as roughly as  $\propto |y - W/2|^{-1}$  as one moves away from the center of the channel along the  $+y$  direction up to  $y = W/2 + L_C$  and decays exponentially thereafter with a decay constant on the order of  $L + L_C$ .

## B. The effect of contact resistance

In devices where  $R_C$  is not negligible, the contact resistance parameter  $r$  has different effects on current fringing, depending on the current transfer length at the contact,  $L_T$ . The voltage drop across a contact happens in a region within about  $L_T$  of the contact perimeter. Consequently, devices with  $L_C \gg L_T$  (i.e.,  $\ell_C \gg \ell_T$ ) have contacts that are *electrically long*. In such devices, a higher  $R_C$  forces the current to spread farther along the sides of the contacts to counteract the increasing voltage drop across contacts as shown in Fig. 4(a) [compare with Fig. 4(b) which shows a device with negligible  $R_C$ ]. This causes fringe current and, hence, the CF and  $i_f$ , to increase with the increasing contact resistance parameter  $r$ , as can be seen in Fig. 4(c).

As an example, from Eqs. (6) and (9), a device with  $W = L_C = 10L$  and negligible  $R_C$  has  $CF_{\text{ideal}} - 1 = (2L/W)i_{f,\text{ideal}} = 26\%$ , which represents current density overestimation due to fringe currents in the “ideal device.” For  $L_T \approx 0$  and  $r = 1$  (which can be viewed as the boundary between the channel-limited and contact-limited regimes), the same device has  $CF - 1 = 51\%$ , rising to  $CF - 1 = 70\%$  and beyond for  $r \geq 2$ . This would represent a substantial overestimation of current density and mobility, if not accounted for. In the extreme limit  $r \gg 1$  (describing a completely contact-limited device, with negligible channel resistance), the current is evenly spread out along the contact perimeter, so the total device

resistance is inversely proportional to (and the current is directly proportional to) the contact perimeter  $W + 2L_C$ . Because this perimeter is simply  $W$  for a patterned device [see Fig. 1(d)], in this limit,  $CF = I/(WJ_{1D}) \cong (W + 2L_C)/W = 1 + 2\ell_C/W$  by Eq. (2) and  $i_f \cong \ell_C$  by Eq. (6).

The current spreading behavior can be substantially different in devices where  $L_T$  is not negligible compared to  $L_C$ , as illustrated in Fig. 4(d). The effect of  $L_T$  is to reduce the effective contact width where the current density is close to its peak value ( $J \cong J_{1D}$ ), which can be seen by comparing Fig. 4(b)–4(e). Increasing  $L_T$  thus decreases the total current and, hence CF and  $i_f$ . In devices with *electrically short* contacts ( $L_C \ll L_T$  or  $\ell_C \ll \ell_T$ ), which can be found in, e.g., in graphene<sup>65</sup> and black phosphorus<sup>66</sup> TFTs (where contacts may have  $L_T > 1 \mu\text{m}$ ), current is spread across the entire contact area  $WL_C$  rather than just the perimeter  $W + 2L_C$ . For  $r \gg 1$  where the channel resistance is negligible, the current flow between the contact metal and the channel is limited by, and thus proportional to, the contact area  $WL_C$  [ $R_{\text{tot}} \cong 2\rho_C/(WL_C)$ ]. A patterned device with the same geometry parameters has the same contact area and, hence, current. Therefore, very large  $r$  and  $\ell_T$  lead to  $CF \cong 1$  and  $i_f \cong 0$ .

If  $R_C$  is not negligible, fringe currents cause device characteristics to differ from those of a patterned device in ways that are more subtle than a constant scaling factor. Consider the transfer characteristics of the partially contact-limited patterned-channel TFT, given as solid lines in Fig. 4(f) (assuming for the moment that  $R_C$  does not depend on  $V_{\text{ov}}$ ). An unpatterned TFT with the same parameters and  $L_T \ll L_C$  (electrically long contacts) yields characteristics [dashed lines in Fig. 4(f)] that differ from those of the patterned device (solid lines) by a CF that depends on  $V_{\text{ov}}$ .

For small  $V_{\text{ov}}$  [the inset of Fig. 4(f)],  $R_C$  can be considered negligible relative to the channel resistance ( $r \ll 1$ ), so the unpatterned device current is greater by about  $CF_{\text{ideal}} - 1 = 2(L/W)i_{f,\text{ideal}} = 54\%$ , from Eqs. (6) and (9). At higher  $V_{\text{ov}}$ , the device begins to become contact dominated, with  $r$  reaching and then exceeding 1. As a result, following the trend in Fig. 4(c), CF increases with  $V_{\text{ov}}$  reaching  $\sim 100\%$  at  $V_{\text{ov}} = 6 \text{ V}$ . This bias-

13 June 2025 19:18:45

**FIG. 3.** (a) Fringe current overestimation  $CF - 1$  (solid lines and square markers, left axis) and normalized fringe current  $i_f$  (dotted lines and triangular markers, right axis) as a function of the aspect ratio  $w = W/L$  for different normalized contact lengths  $\ell_C = L_C/L$ , if  $R_C$  and VS are negligible. The markers are numerical simulation results, the lines are the results of the analytical approximation Eq. (9). (b, c) Top-down view of current density distribution for (b) shorter contacts ( $L_C = 0.5L$ ) and (c) longer contacts ( $L_C = 2L$ ). The current density is normalized to that of a patterned channel TFT [Fig. 1(d)] with the same dimensions. Only a quarter of each device is shown, utilizing the lengthwise and widthwise symmetries.

13 June 2025 19:18:45

**FIG. 4.** (a) The normalized current distribution in a device with resistive, electrically long contacts ( $r=2$ ,  $\ell_T = \ell_T/L \approx 0$ ). Only a quarter of the device geometry is shown. Current is spread farther along the sides of the contacts, so fringe current is considerably higher than (b) a device with  $R_C = 0$ . (c) Normalized fringe current as a function of contact resistance parameter  $r$ , for contact lengths  $L_C = 2L$ ,  $5L$ , and  $10L$ ,  $W/L = 10$ , and  $\ell_T = \ell_T/L \approx 0$  (electrically long device). Dotted lines indicate  $i_{f,ideal}$  [Eq. (9)]. (d) Normalized fringe current as a function of  $r$  and  $\ell_T = \ell_T/L$ , for the same  $L_C$  and  $w$ , showing that the fringe current contribution to total current decreases with contact resistance in electrically short devices ( $L_T \gg L_C$ ). (e) The normalized current distribution in a device with resistive contacts ( $r=2$ ) and  $\ell_T = \ell_T/L = 1$ . Current density drops gradually deep into the contacts, resulting in a reduction of the width of the region between the contacts where maximum current density exists. This can be loosely understood as a reduction in effective contact width, resulting in lower current and, hence, a CF lower than that of a device with negligible  $R_C$  (panel b). (f) Comparison of the transfer characteristics of a patterned-channel TFT (solid lines) with those of an unpatterned-channel (dashed lines). The device parameters are  $L = 1 \mu\text{m}$ ,  $W = 4 \mu\text{m}$ ,  $L_C = 5 \mu\text{m}$ ,  $\mu_n C_{\text{ox}} = 10 \mu\text{A}/\text{V}^2$ ,  $R_C = 30 \text{k}\Omega\cdot\mu\text{m}$ ,  $\ell_T \approx 0$  (electrically long contacts). The contact resistance parameter  $r$  varies with  $V_{\text{ov}}$ , with  $r=0.3$  at  $V_{\text{ov}} = 1 \text{ V}$ . Here, we assume  $R_C$  is independent of  $V_{\text{ov}}$  but the qualitative trends remain valid as long as  $R_C$  varies more slowly with  $V_{\text{ov}}$  than the channel resistance. (g) The same comparison with the same device parameters, except for  $L_T = 100 \mu\text{m} \gg L_C$  (electrically short contacts). The effect of fringe currents on unpatterned device characteristics is suppressed considerably in a device with electrically short contacts compared to long contacts (panel f).

dependent fringe current contribution can have subtle effects like partially masking signs of a contact-limited device. Notice that for low  $V_{\text{DS}}$ , the unpatterned device current fails to asymptote to a constant  $R_C$ -limited value at high  $V_{\text{ov}}$ , but continues to increase along with the CF.

The effect of fringe currents on the characteristics of devices with  $L_T \gg L_C$  (electrically short contacts) is limited in comparison, as can be seen in Fig. 4(g). For small  $V_{\text{ov}}$ , we still have  $\text{CF}_{\text{ideal}} - 1 = 54\%$  as in Fig. 4(f). The device again becomes contact limited at high  $V_{\text{ov}}$ , but following Fig. 4(d) for large  $\ell_T$ , CF decreases. The patterned and unpatterned characteristics thus approximately converge at high  $V_{\text{ov}}$ . It should be mentioned that while the assumption of  $V_{\text{ov}}$ -independent  $R_C$  can work well in, e.g., top-contacted, top-gated devices where the

contacts shield the semiconductor underneath from the gate influence, it is likely to fail in, e.g., back-gated devices in which the contacts are “gated.” Thus, the gate bias dependence of CF and  $i_f$  is also influenced by the device structure. Finally, for non-zero  $R_C$ ,  $V_{\text{ov}}$  and  $V_{\text{DS}}$  also have a weak influence on CF via the bias parameter  $v$ , which will be discussed in Sec. III D.

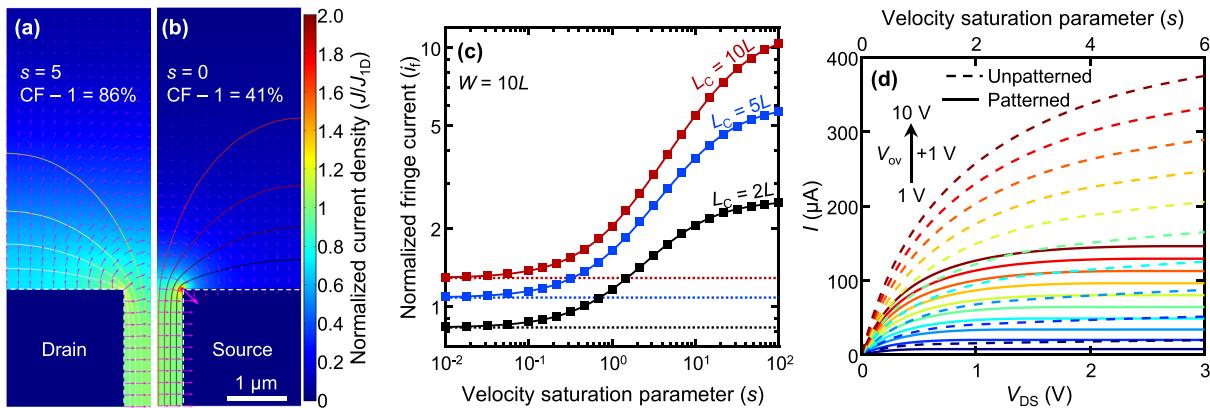

### C. The effect of velocity saturation

In devices that are impacted by VS (i.e., where  $s$  is not negligible), current seeks roundabout pathways that avoid regions of the channel with high lateral field, which have higher sheet resistance. In other words, because the shortest lateral distance between

contacts has the highest field (comparable to or greater than  $E_c$ ), this is also the most resistive region, forcing more of the current to take fringing paths that have lower lateral fields and thus lower resistivity. The result is more fringe current spreading than in a device with negligible VS, as can be seen by comparing Figs. 5(a) and 5(b) and, hence, a higher CF and  $i_f$  as shown in Fig. 5(c). The impact of VS on fringe current is thus similar to that of  $R_C$  with electrically long contacts ( $L_C \gg L_T$  or  $\ell_C \gg \ell_T$ ).

Like  $R_C$ , VS in unpatterned-channel devices can cause device characteristics to deviate substantially from expected behavior. Increasing  $V_{DS}$  increases the average lateral field in the channel, and hence  $s$ , causing the CF and current to increase. This is illustrated in Fig. 5(d), which compares the output characteristics of unpatterned- and patterned-channel devices whose currents are limited by VS, as can be discerned from the evenly spaced saturation currents for increasing  $V_{ov}$ . Due to the  $V_{DS}$  dependence of CF through the VS parameter  $s$ , the current of the unpatterned-channel device continues to increase with  $V_{DS}$  even after the device reaches the pinch-off, thus reducing the device output resistance  $(\partial I / \partial V_{DS})^{-1}$ . As with  $V_{ov}$ , increasing  $V_{DS}$  also influences the CF via the bias parameter  $v$ , but this happens to be a negligible effect as will be discussed in Sec. III D.

#### D. The effect of the bias parameter

In this section, we take a closer look at the weak dependence of CF on the bias regime (i.e.,  $v = V_{DS}/V_{ov}$ ) that has been noted in the literature.<sup>2,32</sup> When VS is negligible ( $s = 0$ ) and  $V_{DS} \ll V_{ov}$ , the sheet conductance  $G_{sh}^0 = \mu_n C_{ox} V_{ov}$  in the channel is uniform and the electrostatic potential  $V$  in the channel obeys Laplace's equation  $\nabla^2 V = 0$ , with the current density given by  $\mathbf{J} = -G_{sh}^0 \nabla V$  (Ohm's law with uniform sheet conductance, see Eq. (S7) of Sec. S2 in the supplementary material). For more general bias conditions, however ( $v = V_{DS}/V_{ov} > 0$ ), the channel potential obeys the nonlinear Eq. (S8) of Sec. S4 in the supplementary material, with  $\mathbf{J} = -G_{sh} \nabla V = -\mu_n C_{ox} (V_{ov} - V) \nabla V$ . We can define an effective

potential  $\phi = [1 - V/(2V_{ov})]V$  in terms of the channel potential, which reduces Eq. (S8) in the supplementary material to Laplace's equation  $\nabla^2 \phi = 0$ , even when  $V_{DS}$  is not much smaller than  $V_{ov}$ . Moreover, the current density can then be expressed as  $\mathbf{J} = -G_{sh}^0 \nabla \phi$ , a form identical to that in a device that has uniform sheet conductance  $G_{sh}^0$ , with  $V$  replaced by  $\phi$ .

Furthermore, if we have negligible  $R_C$  ( $r = 0$ ), then the drain and source contacts simply become Dirichlet boundary conditions  $\phi = (1 - v/2)V_{DS}$  and  $\phi = 0$ , respectively. Thus, the problem is reduced to one in which current flows in a channel with uniform sheet conductance  $G_{sh}^0$ , with potential difference  $(1 - v/2)V_{DS}$  applied across it. Since  $v = V_{DS}/V_{ov}$  affects the voltage applied across this channel but not its sheet conductance, it has no effect on the "shape" of current distribution, so it does not affect CF. Thus, the results of Sec. III A apply equally well when  $v$  is not negligible, as long as  $R_C$  and VS are negligible. The fact that the shape of current distribution does not depend on  $V_{DS}$  is illustrated in Figs. 6(a) and 6(b).

When  $R_C$  is appreciable ( $r > 0$ ) with electrically long contacts ( $L_T \ll L_C$ ), the current tends to spread out along the contact perimeter in response, as discussed in Sec. III B. However, when the device is in or close to the saturation regime ( $v > 0$ ), the current cannot spread out along the drain perimeter as effectively because the high channel potential near the drain increases the sheet resistance here. Thus, the current does not spread out as much and the CF is reduced, as can be seen by comparing Figs. 6(c) and 6(d). The reduction of  $i_f$  with the bias parameter  $v$  is given in Fig. 6(e), which shows that  $v$  has a relatively weak influence on current spreading, peaking at around  $r \approx 3$ , where the device current is severely contact-limited. We may, thus, at least partially attribute the small reduction of CF in the saturation regime observed in Ref. 2 (where a bias-dependent  $r > 0.1$  was estimated) to  $R_C$ .

The bias parameter has a similar but much weaker effect on the fringe current in TFTs that are affected by VS as shown in

**FIG. 5.** (a) The normalized current distribution in a device with VS parameter  $s = 5$ . Fringe current is considerably higher than (b) a device without VS. (c) Normalized fringe current as a function of  $s$ , for several different contact lengths and  $w = W/L = 10$ . The dotted lines indicate  $i_{f,ideal}$  [Eq. (9)]. (d) The output characteristics of patterned- (solid lines) and unpatterned-channel (dashed lines) TFTs with VS. The device parameters are  $L = 1 \mu\text{m}$ ,  $W = 4 \mu\text{m}$ ,  $L_C = 5 \mu\text{m}$ ,  $\mu_n C_{ox} = 10 \mu\text{A/V}^2$  and  $E_c = 5 \text{ kV/cm}$ , corresponding to  $s = 2$  at  $V_{DS} = 1 \text{ V}$ . The unpatterned device current is higher by  $CF - 1 \geq 54\%$  due to fringe currents. This factor rises to 160% with increasing  $V_{DS}$ , caused by increased VS in the channel (higher  $s$ ).

13 June 2025 19:18:45

**FIG. 6.** (a) Current distribution and equipotential lines in a device at the edge of saturation ( $V_{ov} = V_{DS} = 1$  V). Note that the current density is symmetric, even though the channel is pinched off near the drain contact. (b) Current distribution in the same device, where the lines correspond to equally spaced contours of a constant effective potential  $\phi = [1 - V/(2V_{ov})]V$  instead, where  $V$  is the electrostatic potential. These lines are exactly the same as the equipotential lines in a device with  $V_{DS} \ll V_{ov}$  [see Fig. 3(c)], and the normalized current distribution is likewise identical as it is proportional to  $-\nabla\phi$ . (c) The current distribution in a device with contact resistance parameter  $r = 2$  biased at pinch-off ( $V_{DS} = V_{ov}$ ). The black lines are contours of equal current density to aid in the visualization of reduced current spreading along the side of the drain compared to the source. (d) The same device with  $V_{DS} \ll V_{ov}$  is used for reference. (e) Normalized fringe current  $i_f$  as a function of bias parameter  $v = V_{DS}/V_{ov}$  for different contact resistance parameters  $r$  and electrically long contacts ( $L_T \ll L_C$ ).  $r$  is spaced logarithmically by 2 steps/decade and labeled on the curves. (f)  $i_f$  as a function of  $v$  for several velocity saturation VS parameters  $s$ .  $s$  is spaced logarithmically by 2 steps/decade and labeled on the curves.  $v$  is varied up to the point the device enters the saturation regime, which occurs at  $v < 1$  because VS results in  $V_{DS,sat} < V_{ov}$ .

13 June 2025 19:18:45

Fig. 6(f): the reduction of normalized fringe current  $i_f$  at saturation, relative to its value at  $v = 0$ , is less than 1%. Finally, we stress that the relatively weak influence of  $v$  on  $i_f$  should not be understood to mean that the bias voltages cannot affect current spreading or device characteristics appreciably because, as noted in Secs. III B and III C,  $R_C$  and VS parameters  $r$  and  $s$  also depend on  $V_{ov}$  and  $V_{DS}$ , respectively.

#### IV. CONCLUSIONS

Through an analytical model and simulations, we have quantified the influence of geometry, bias, and transport properties on fringe currents in thin-film transistors without a channel patterned into a rectangular strip narrower than the contacts. If not corrected, the fringe current contribution causes current density and mobility to be overestimated. For unpatterned-channel transistors, we presented the first systematic analysis of resistive contacts (including transfer length) and velocity saturation, which affect advanced short-channel devices. We have shown that each can more than double the

relative contribution of fringe currents, causing up to 70% mobility overestimation in typical unpatterned devices. Furthermore, the relative contribution of fringe currents in such devices is bias-dependent, which can confound the interpretation of measured device characteristics and the extraction of transport parameters. In particular, current spreading can obscure signs of high contact resistance in device measurements, or degrade the output resistance  $(\partial I/\partial V_{DS})^{-1}$  in devices that suffer from velocity saturation.

Fortunately, these effects can at least partially be accounted for through simulations for a more reliable extraction of performance metrics. In the particular case of devices where contact resistance and velocity saturation are negligible, we have shown that bias voltages do not influence the fringe current contribution, and that current density and mobility can be calculated with ease—without look-up tables or iterative methods—using a very accurate analytical expression for the correction factor. Nonetheless, it is advisable to properly pattern the transistor channel whenever possible. If this proves impractical, contacts should be defined with  $W/L > 100$ , which limits the fringe current contribution to < 7% in most cases.

## SUPPLEMENTARY MATERIAL

See the [supplementary material](#) that includes (1) details of the experimental procedure for mapping current density; (2) an example that reassesses the fringe current correction attempt of our prior experimental work<sup>22</sup> where velocity saturation was neglected; (3) closed-form expressions for the drain current and saturation voltage for a patterned-channel transistor; (4) the general formulation of the 2D current flow problem in an unpatterned-channel TFT; (5) a demonstration that the dimensionless parameters in [Table I](#) uniquely characterize the “shape” of current distribution in an unpatterned TFT; (6) an exact derivation of the fringe current in an infinitely wide unpatterned TFT; and (7) quantitative details of the decay of current density away from the contacts.

## ACKNOWLEDGMENTS

This work was supported, in part, by the Stanford SystemX Alliance, as well as by SUPREME and PRISM, two of the seven centers in JUMP 2.0, a Semiconductor Research Corporation (SRC) program sponsored by DARPA. S.W. also acknowledges support from a Stanford Graduate Fellowship (SGF). A.D. acknowledges funding by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) through the Emmy Noether Programme (No. 506140715).

## AUTHOR DECLARATIONS

## Conflict of Interest

The authors have no conflicts to disclose.

## Author Contributions

**Çağrı Körögü:** Conceptualization (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Visualization (equal); Writing – original draft (equal); Writing – review & editing (equal). **Alwin Daus:** Conceptualization (equal); Supervision (supporting); Writing – review & editing (equal). **Sumaiya Wahid:** Resources (lead); Writing – review & editing (supporting). **Miguel Muñoz Rojo:** Writing – review & editing (supporting). **Eric Pop:** Conceptualization (equal); Funding acquisition (equal); Supervision (equal); Writing – review & editing (equal).

## DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## REFERENCES

- <sup>1</sup>C. Bartic, H. Jansen, A. Campitelli, and S. Borghs, “Ta<sub>2</sub>O<sub>5</sub> as gate dielectric material for low-voltage organic thin-film transistors,” *Org. Electron.* **3**(2), 65–72 (2002).

- <sup>2</sup>K. Pei, M. Chen, Z. Zhou, H. Li, and P. K. L. Chan, “Overestimation of carrier mobility in organic thin film transistors due to unaccounted fringe currents,” *ACS Appl. Electron. Mater.* **1**(3), 379–388 (2019).

- <sup>3</sup>F. Shan, A. Liu, H. Zhu, W. Kong, J. Liu, B. Shin, E. Fortunato, R. Martins, and G. Liu, “High-mobility p-type NiO<sub>x</sub> thin-film transistors processed at low temperatures with Al<sub>2</sub>O<sub>3</sub> high-k dielectric,” *J. Mater. Chem. C* **4**(40), 9438–9444 (2016).

- <sup>4</sup>R. A. John, N. A. Chien, S. Shukla, N. Tiwari, C. Shi, N. G. Ing, and N. Mathews, “Low-temperature chemical transformations for high-performance solution-processed oxide transistors,” *Chem. Mater.* **28**(22), 8305–8313 (2016).

- <sup>5</sup>I. Isakov, H. Faber, M. Grell, G. Wyatt-Moon, N. Pliatsikas, T. Kehagias, G. P. Dimitrakopoulos, P. P. Patsalas, R. Li, and T. D. Anthopoulos, “Exploring the Leidenfrost effect for the deposition of high-quality In<sub>2</sub>O<sub>3</sub> layers via spray pyrolysis at low temperatures and their application in high electron mobility transistors,” *Adv. Funct. Mater.* **27**(22), 1606407 (2017).

- <sup>6</sup>C. R. Kagan, D. B. Mitzi, and C. D. Dimitrakopoulos, “Organic-inorganic hybrid materials as semiconducting channels in thin-film field-effect transistors,” *Science* **286**(5441), 945–947 (1999).

- <sup>7</sup>D. B. Mitzi, C. D. Dimitrakopoulos, J. Rosner, D. R. Medeiros, Z. Xu, and C. Noyan, “Hybrid field-effect transistor based on a low-temperature melt-processed channel layer,” *Adv. Mater.* **14**(23), 1772–1776 (2002).

- <sup>8</sup>T. Matsushima, K. Fujita, and T. Tsutsui, “High field-effect hole mobility in organic-inorganic hybrid thin films prepared by vacuum vapor deposition technique,” *Jpn. J. Appl. Phys.* **43**(9A), L1199 (2004).

- <sup>9</sup>T. Matsushima, S. Hwang, A. S. D. Sandanayaka, C. Qin, S. Terakawa, T. Fujihara, M. Yahiro, and C. Adachi, “Solution-processed organic–inorganic perovskite field-effect transistors with high hole mobilities,” *Adv. Mater.* **28**(46), 10275–10281 (2016).

- <sup>10</sup>Y. Wu, J. Li, J. Xu, Y. Du, L. Huang, J. Ni, H. Cai, and J. Zhang, “Organic–inorganic hybrid CH<sub>3</sub>NH<sub>3</sub>PbI<sub>3</sub> perovskite materials as channels in thin-film field-effect transistors,” *RSC Adv.* **6**(20), 16243–16249 (2016).

- <sup>11</sup>S. P. Senanayak, K. Dey, R. Shivanna, W. Li, D. Ghosh, Y. Zhang, B. Roose, S. J. Zelewski, Z. Andaji-Garmaroudi, W. Wood, N. Tiwale, J. L. MacManus-Driscoll, R. H. Friend, S. D. Stranks, and H. Sirringhaus, “Charge transport in mixed metal halide perovskite semiconductors,” *Nat. Mater.* **22**(2), 216–224 (2023).

- <sup>12</sup>C. Berger, Z. Song, T. Li, X. Li, A. Y. Ogbazghi, R. Feng, Z. Dai, A. N. Marchenkov, E. H. Conrad, P. N. First, and W. A. de Heer, “Ultrathin epitaxial graphite: 2D electron gas properties and a route toward graphene-based nanoelectronics,” *J. Phys. Chem. B* **108**(52), 19912–19916 (2004).

- <sup>13</sup>T. J. Echtermeyer, M. C. Lemme, J. Bolten, M. Baus, M. Ramsteiner, and H. Kurz, “Graphene field-effect devices,” *Eur. Phys. J. Spec. Topics* **148**(1), 19–26 (2007).

- <sup>14</sup>M. C. Lemme, T. J. Echtermeyer, M. Baus, B. N. Szafranek, J. Bolten, M. Schmidt, T. Wahlbrink, and H. Kurz, “Mobility in graphene double gate field effect transistors,” *Solid-State Electron.* **52**(4), 514–518 (2008).

- <sup>15</sup>I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. L. Shepard, “Graphene field-effect transistors based on boron nitride gate dielectrics,” in *IEEE International Electron Devices Meeting* (IEEE, 2010), pp. 23.2.1–23.2.4.

- <sup>16</sup>Y. K. Koh, A. S. Lyons, M.-H. Bae, B. Huang, V. E. Dorgan, D. G. Cahill, and E. Pop, “Role of remote interfacial phonon (RIP) scattering in heat transport across graphene/SiO<sub>2</sub> interfaces,” *Nano Lett.* **16**(10), 6014–6020 (2016).

- <sup>17</sup>L. Li, Y. Yu, G. J. Ye, Q. Ge, X. Ou, H. Wu, D. Feng, X. H. Chen, and Y. Zhang, “Black phosphorus field-effect transistors,” *Nat. Nanotechnol.* **9**(5), 372–377 (2014).

- <sup>18</sup>J. D. Wood, S. A. Wells, D. Jariwala, K.-S. Chen, E. Cho, V. K. Sangwan, X. Liu, L. J. Lauhon, T. J. Marks, and M. C. Hersam, “Effective passivation of exfoliated black phosphorus transistors against ambient degradation,” *Nano Lett.* **14**(12), 6964–6970 (2014).

- <sup>19</sup>A. V. Penumatcha, R. B. Salazar, and J. Appenzeller, “Analysing black phosphorus transistors using an analytic Schottky barrier MOSFET model,” *Nat. Commun.* **6**(1), 8948 (2015).

- <sup>20</sup>N. Haratipour, S. Namgung, S.-H. Oh, and S. J. Koester, “Fundamental limits on the subthreshold slope in Schottky source/drain black phosphorus field-effect transistors,” *ACS Nano* **10**(3), 3791–3800 (2016).

- <sup>21</sup>S. J. Choi, B.-K. Kim, T.-H. Lee, Y. H. Kim, Z. Li, E. Pop, J.-J. Kim, J. H. Song, and M.-H. Bae, “Electrical and thermoelectric transport by variable range hopping in thin black phosphorus devices,” *Nano Lett.* **16**(7), 3969–3975 (2016).

- <sup>22</sup>A. Daus, S. Vaziri, V. Chen, Ç Körögü, R. W. Grady, C. S. Bailey, H. R. Lee, K. Schauble, K. Brenner, and E. Pop, “High-performance flexible nanoscale transistors based on transition metal dichalcogenides,” *Nat. Electron.* **4**(7), 495–501 (2021).

<sup>23</sup>H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P. D. Ye, "Phosphorene: An unexplored 2D semiconductor with a high hole mobility," *ACS Nano* **8**(4), 4033–4041 (2014).

<sup>24</sup>H. C. P. Movva, A. Rai, S. Kang, K. Kim, B. Fallahazad, T. Taniguchi, K. Watanabe, E. Tutuc, and S. K. Banerjee, "High-mobility holes in dual-gated WSe<sub>2</sub> field-effect transistors," *ACS Nano* **9**(10), 10402–10410 (2015).

<sup>25</sup>G. Qiu, Y. Du, A. Charnas, H. Zhou, S. Jin, Z. Luo, D. Y. Zemlyanov, X. Xu, G. J. Cheng, and P. D. Ye, "Observation of optical and electrical in-plane anisotropy in high-mobility few-layer ZrTe<sub>5</sub>," *Nano Lett.* **16**(12), 7364–7369 (2016).

<sup>26</sup>T. M. Higgins, S. Finn, M. Matthiesen, S. Grieger, K. Synnatschke, M. Brohmann, M. Rother, C. Backes, and J. Zaumseil, "Electrolyte-gated n-type transistors produced from aqueous inks of WS<sub>2</sub> nanosheets," *Adv. Funct. Mater.* **29**(4), 1804387 (2019).

<sup>27</sup>V. T. Vu, T. T. H. Vu, T. L. Phan, W. T. Kang, Y. R. Kim, M. D. Tran, H. T. T. Nguyen, Y. H. Lee, and W. J. Yu, "One-step synthesis of NbSe<sub>2</sub>/Nb-doped-WSe<sub>2</sub> metal/doped-semiconductor van der Waals heterostructures for doping controlled ohmic contact," *ACS Nano* **15**(8), 13031–13040 (2021).

<sup>28</sup>V. T. Vu, T. L. Phan, T. T. H. Vu, M. H. Park, V. D. Do, V. Q. Bui, K. Kim, Y. H. Lee, and W. J. Yu, "Synthesis of a selectively Nb-doped WS<sub>2</sub>–MoS<sub>2</sub> lateral heterostructure for a high-detectivity PN photodiode," *ACS Nano* **16**(8), 12073–12082 (2022).

<sup>29</sup>S.-S. Wani, C. C. Hsu, Y.-Z. Kuo, K. M. M. Darshana Kumara Kimbulapitiya, C.-C. Chung, R.-H. Cyu, C.-T. Chen, M.-J. Liu, M. Chaudhary, P.-W. Chiu, Y.-L. Zhong, and Y.-L. Chueh, "Enhanced electrical transport properties of molybdenum disulfide field-effect transistors by using alkali metal fluorides as dielectric capping layers," *ACS Nano* **18**(16), 10776–10787 (2024).

<sup>30</sup>S. Lee, Y. Chen, J. Jeon, C. Park, and J. Jang, "Reduction of parasitic capacitance in indium-gallium-zinc oxide (a-IGZO) thin-film transistors (TFTs) without sacrificing drain currents by using stripe-patterned source/drain electrodes," *Adv. Electron. Mater.* **4**(4), 1700550 (2018).

<sup>31</sup>N. S. Khaanghah, D. Corsino, F. Catania, J. Costa, G. Cantarella, and N. Münzenrieder, "Influence of semiconductor island geometry on the AC performance of flexible InGaZnO TFTs," *IEEE Electron Device Lett.* **44**(5), 773–776 (2023).

<sup>32</sup>C. Chen, Z. Chen, K. Xu, J. Zheng, H. Ou, Z. Wang, H. Chen, X. Liu, Q. Wu, P. K. L. Chan, and C. Liu, "Thin-film transistors with the fringe effect and the correction factor for mobility extraction," *IEEE Electron Device Lett.* **40**(6), 897–900 (2019).

<sup>33</sup>S. Wahid, A. Daus, J. Kwon, S. Qin, J.-S. Ko, H.-S. P. Wong, and E. Pop, "Effect of top-gate dielectric deposition on the performance of indium tin oxide transistors," *IEEE Electron Device Lett.* **44**(6), 951–954 (2023).

<sup>34</sup>Y. Zhang, W. Zhu, F. Hui, M. Lanza, T. Borca-Tasciuc, and M. Muñoz Rojo, "A review on principles and applications of scanning thermal microscopy (SThM)," *Adv. Funct. Mater.* **30**(18), 1900892 (2020).

<sup>35</sup>F. Menges, P. Mensch, H. Schmid, H. Riel, A. Stemmer, and B. Gotsmann, "Temperature mapping of operating nanoscale devices by scanning probe thermometry," *Nat. Commun.* **7**(1), 10874 (2016).

<sup>36</sup>A. A. Wilson, M. Muñoz Rojo, B. Abad, J. Andrés Perez, J. Maiz, J. Schomacker, M. Martín-Gonzalez, D.-A. Borca-Tasciuc, and T. Borca-Tasciuc, "Thermal conductivity measurements of high and low thermal conductivity films using a scanning hot probe method in the 3ω mode and novel calibration strategies," *Nanoscale* **7**(37), 15404–15412 (2015).

<sup>37</sup>M. Muñoz Rojo, S. Grauby, J.-M. Rampoux, O. Caballero-Calero, M. Martín-Gonzalez, and S. Dilhaire, "Fabrication of Bi<sub>2</sub>Te<sub>3</sub> nanowire arrays and thermal conductivity measurement by 3ω-scanning thermal microscopy," *J. Appl. Phys.* **113**(5), 054308 (2013).

<sup>38</sup>K. Okamura, D. Nikolova, N. Mechau, and H. Hahn, "Appropriate choice of channel ratio in thin-film transistors for the exact determination of field-effect mobility," *Appl. Phys. Lett.* **94**(18), 183503 (2009).

<sup>39</sup>H. M. Dipu Kabir, Z. Ahmed, R. Kariyadan, L. Zhang, and M. Chan, "Modeling of fringe current for semiconductor-extended organic TFTs," in *IEEE International Conference on Electron Devices and Solid-State Circuits* (IEEE, 2016), pp. 177–180.

<sup>40</sup>W. Shockley, "Hot electrons in germanium and Ohm's law," *Bell Syst. Techn. J.* **30**(4), 990–1034 (1951).

<sup>41</sup>D. M. Caughey and R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE* **55**(12), 2192–2193 (1967).

<sup>42</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed. (John Wiley & Sons, Inc., Hoboken, NJ, 2007).

<sup>43</sup>J. A. del Alamo, *Integrated Microelectronic Devices: Physics and Modeling*, 1st ed. (Pearson, New York, NY, 2017).

<sup>44</sup>C. Canali, G. Majni, R. Minder, and G. Ottaviani, "Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature," *IEEE Trans. Electron Devices* **22**(11), 1045–1047 (1975).

<sup>45</sup>K. K. Thornber, "Relation of drift velocity to low-field mobility and high-field saturation velocity," *J. Appl. Phys.* **51**(4), 2127–2136 (1980).

<sup>46</sup>T. Leroux, "Static and dynamic analysis of amorphous-silicon field-effect transistors," *Solid-State Electron.* **29**(1), 47–58 (1986).

<sup>47</sup>K. K. H. Smithe, C. D. English, S. V. Suryavanshi, and E. Pop, "High-field transport and velocity saturation in synthetic monolayer MoS<sub>2</sub>," *Nano Lett.* **18**(7), 4516–4522 (2018).

<sup>48</sup>V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Appl. Phys. Lett.* **97**(8), 082112 (2010).

<sup>49</sup>X. Wang and A. Dodabalapur, "Carrier velocity in amorphous metal-oxide-semiconductor transistors," *IEEE Trans. Electron Devices* **68**(1), 125–131 (2021).

<sup>50</sup>W. Warta and N. Karl, "Hot holes in naphthalene: High, electric-field-dependent mobilities," *Phys. Rev. B* **32**(2), 1172–1182 (1985).

<sup>51</sup>N. Karl, "Charge carrier transport in organic semiconductors," *Synth. Met.* **133**–**134**, 649–657 (2003).

<sup>52</sup>H. Berger, "Contact resistance on diffused resistors," in *IEEE International Solid-State Circuits Conference* (IEEE, 1969), pp. 160–161.

<sup>53</sup>H. Murrmann and D. Widmann, "Current crowding on metal contacts to planer devices," in *IEEE International Solid-State Circuits Conference* (IEEE, 1969), pp. 162–163.

<sup>54</sup>D. K. Schröder, *Semiconductor Material and Device Characterization*, 3rd ed. (John Wiley & Sons, Inc., Hoboken, NJ, 2006).

<sup>55</sup>J. Brown and R. Churchill, *Complex Variables and Applications*, 9th ed. (McGraw Hill, New York, 2013).

<sup>56</sup>J. C. Maxwell, *A Treatise on Electricity and Magnetism* (Clarendon Press, Oxford, 1873).

<sup>57</sup>J. J. Thomson, *Notes on Recent Researches in Electricity and Magnetism Intended as a Sequel to Professor Clerk-Maxwell's Treatise on Electricity and Magnetism* (Clarendon Press, Oxford, 1893).

<sup>58</sup>J. D. Jackson, *Classical Electrodynamics*, 3rd ed. (John Wiley & Sons, Inc., New York, 1999).

<sup>59</sup>R.-L. Lin, "Explicit full field analytic solutions for two-dimensional heat conduction problems with finite dimensions," *Int. J. Heat Mass Transf.* **53**(9), 1882–1892 (2010).

<sup>60</sup>J. Li, M. Tang, and J. Mao, "Analytical thermal model for AlGaN/GaN HEMTs using conformal mapping method," *IEEE Trans. Electron Devices* **69**(5), 2313–2318 (2022).

<sup>61</sup>N. D. Halsey, "Potential flow analysis of multielement airfoils using conformal mapping," *AIAA J* **17**(12), 1281–1288 (1979).

<sup>62</sup>P. K. Kythe, *Handbook of Conformal Mappings and Applications* (Chapman and Hall/CRC, New York, 2019).

<sup>63</sup>W. R. Smythe, *Static and Dynamic Electricity* (McGraw-Hill Book Company, Inc., New York, 1950).

<sup>64</sup>S. B. Cohn, "Characteristic impedance of the shielded-strip transmission line," *IEEE Trans. Microw. Theory Techn.* **2**(2), 52–57 (1954).

<sup>65</sup>A. Venugopal, L. Colombo, and E. M. Vogel, "Contact resistance in few and multilayer graphene devices," *Appl. Phys. Lett.* **96**(1), 013512 (2010).

<sup>66</sup>Y. Du, H. Liu, Y. Deng, and P. D. Ye, "Device perspective for black phosphorus field-effect transistors: Contact resistance, ambipolar behavior, and scaling," *ACS Nano* **8**(10), 10035–10042 (2014).

## SUPPLEMENTARY MATERIAL

### Fringe Current Correction for Unpatterned-Channel Thin-Film Transistors Including Contact Resistance and Velocity Saturation Effects

Çağıl Körögöl<sup>1</sup>, Alwin Daus<sup>2</sup>, Sumaiya Wahid<sup>1</sup>, Miguel Muñoz Rojo<sup>3</sup>, and Eric Pop<sup>1,4,5,\*</sup>

<sup>1</sup>*Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA*

<sup>2</sup>*Institute of Semiconductor Engineering, University of Stuttgart, Stuttgart 70569, Germany*

<sup>3</sup>*2D Foundry, Instituto de Ciencia de Materiales de Madrid (ICMM), CSIC, Madrid 28049, Spain*

<sup>4</sup>*Department of Materials Science & Engineering, Stanford University, Stanford, CA 94305, USA*

<sup>5</sup>*Department of Applied Physics, Stanford University, Stanford, CA 94305, USA*

\*Contact: [epop@stanford.edu](mailto:epop@stanford.edu)

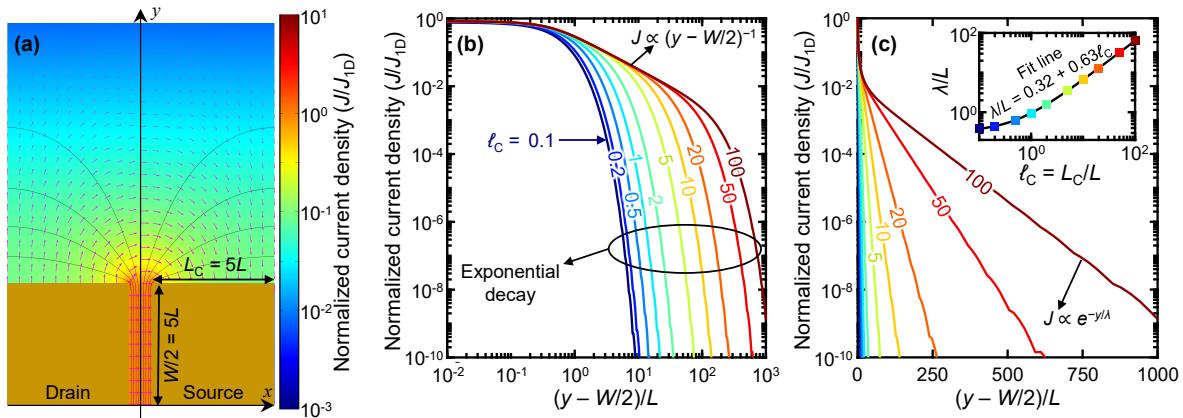

#### S1. EXPERIMENTALLY VISUALIZING CURRENT DENSITY

We experimentally visualize current spreading in back-gated indium tin oxide (ITO) transistors, whose cross section is pictured in Fig. S1(a), by exploiting their self-heating. The devices use  $p^{++}$  Si as the back-gate, and are capped with  $\sim 6$  nm of  $\text{AlO}_x$  to electrically isolate the surface of the sample from the temperature probe scanning over it. Further information on the devices and their fabrication process can be found in Ref. 1. We use one device with channel wider than contacts as in Fig. 1(c) (henceforth referred to as the “unpatterned” device for brevity), and one with channel patterned narrower than contacts as in Fig. 1(d). The simulated temperature rise distribution at the top of the latter device is shown in Fig. S1(b). It can be seen that the temperature is almost uniform over the channel, and quickly decays to zero once we step off the channel, over a distance no more than a few hundred nm.

Some heat spreading occurs in  $\text{AlO}_x$ , ITO and the considerably thicker  $\text{SiO}_2$  underneath, which causes the device temperature distribution to be “smeared out” or “blurred” compared to the distribution of power density (heat generated per unit area). The amount of blurring is quantified by the thermal healing length associated with the lateral heat transport in these layers,<sup>2,3</sup> which in this case is on the order of the  $\text{SiO}_2$  thickness (because the ultrathin ITO thermal conductivity is not much greater than that of  $\text{SiO}_2$ ). As the

**Fig. S1.** (a) Cross-section of the measured ITO devices. (b) Simulated normalized temperature rise at the top of a patterned back-gated ITO device.

thermal healing length is small compared to contact width ( $\sim 8 \mu\text{m}$ ) and channel length ( $\sim 2 \mu\text{m}$ ), the temperature distribution over the channel is a relatively faithful representation of power density in the channel, as Fig. S1(b) confirms.

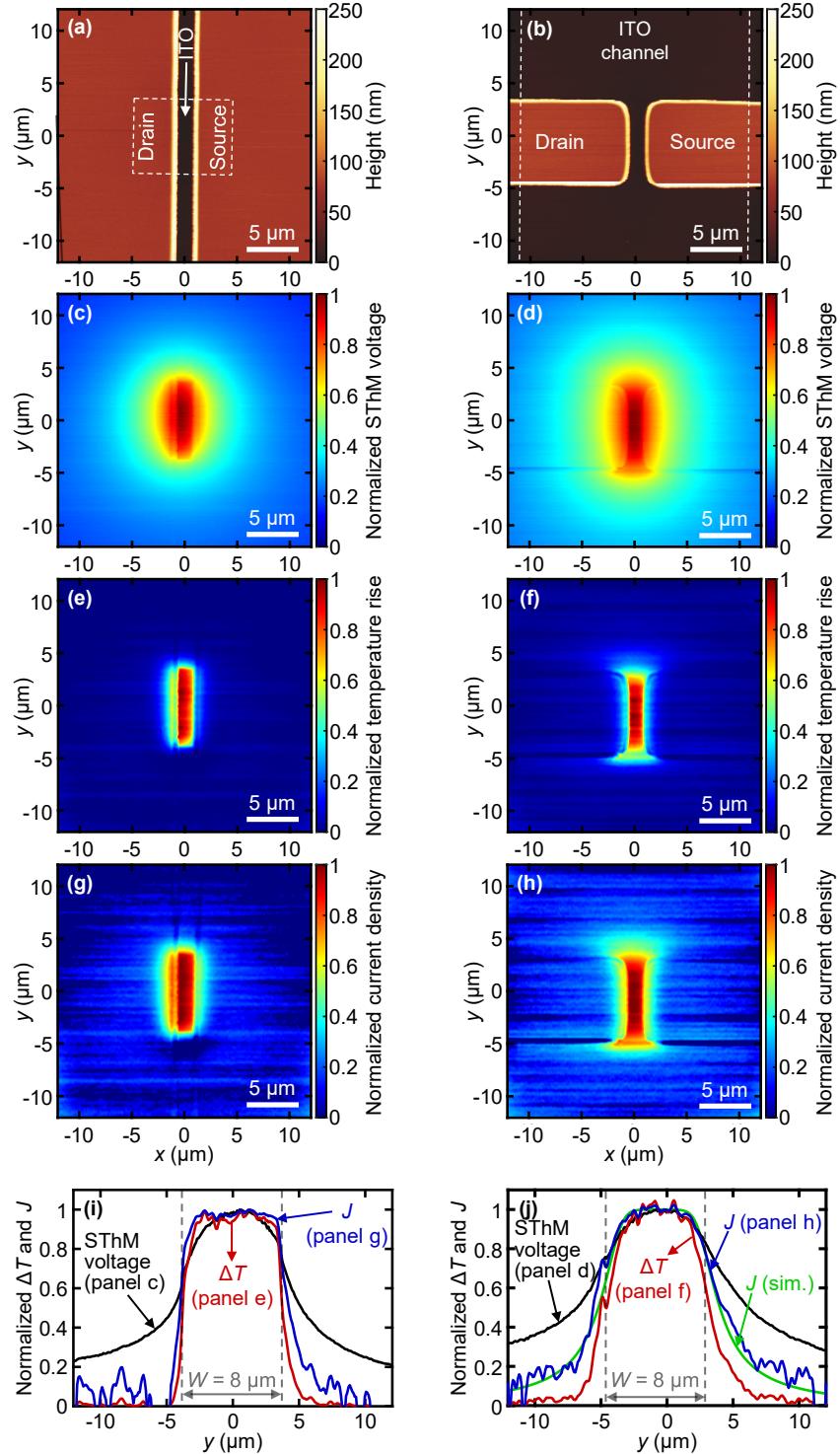

We use scanning thermal microscopy (SThM)<sup>4-7</sup> to map the temperature rise over each device. SThM is a scanning probe technique in which a special atomic force microscope probe with a two-terminal thermometer built into its tip is scanned across the sample while in contact with it. The height of and the voltage across the tip (referred to as the SThM voltage, linearly related to sample temperature) are measured during the scan, allowing the sample topography and surface temperature to be mapped simultaneously. The topography maps are given in Fig. S2(a), S2(b), and the SThM voltages in Fig. S2(c), S2(d), for the patterned and unpatterned devices, respectively. A comparison of Fig. S1(b) and Fig. S2(c) makes it clear that the SThM voltage decays much slower than the simulated temperature as one moves away from the patterned channel, with a long tail proportional to  $1/r$ , where  $r$  is the distance from the device center. This is believed to be a sign of the fact that the heat exchange between the SThM probe and the sample is not localized solely to the point of contact, which causes the measurement to be blurred. Note that the tip of the SThM probe is approximately conical in shape. Since the distance between the cone and the sample increases linearly with distance from the point of contact, we may expect the thermal conductance between the probe and the sample to be approximately inversely proportional to the distance. This explains the prominent  $1/r$  tail present in Fig. S2(c).

The tail is large enough to wash out the effects of heat generated by fringe currents, so a procedure is required to back out the true temperature distribution from the SThM voltage maps. To do this, we first assume that the thermal interaction of the probe with the sample is described by a circularly symmetric impulse response by which the true temperature distribution is smeared out. The assumed form of the impulse response is

$$h(\rho) = \frac{a_1}{1 + \rho/b_1} + \frac{a_2}{b_2} e^{-\frac{\rho}{b_2}} \quad (\text{S1})$$

where  $\rho$  is the horizontal distance from the point of contact between the probe tip. The first term captures both the long-range interaction responsible for the  $1/r$  tail mentioned above as well as the sharp peak of the interaction at the tip (where  $h(\rho) \cong a_1$ ), while the second term can capture intermediate-range interaction taking place within a radius  $\sim b_2$  of the tip. The parameters  $a_1$ ,  $a_2$ ,  $b_1$ ,  $b_2$  are determined such that the simulated temperature distribution in Fig. S1(b), convolved with Eq. (S1), fits Fig. S2(c) with minimum mean squared error.

Having obtained the probe impulse response, we implement a Wiener deconvolution filter,<sup>8</sup> which is used to “unblur” the SThM voltage maps to reproduce the temperature rise (and hence the power density) as accurately possible.<sup>9</sup> The resulting normalized temperature rise maps in the patterned and unpatterned devices are given in Fig. S2(e) and S2(f). Note that the local temperature rise (and power density) is  $J^2/G_{\text{sh}}$ , where  $J$  is the local current density and  $G_{\text{sh}}$  is the sheet conductance. The devices are biased in deep linear region ( $V_{\text{DS}} \ll V_{\text{GS}}$ ), so  $G_{\text{sh}} \cong G_{\text{sh}}^0$  is nearly constant in the channel, making the local current density is proportional to the square root of the temperature rise (this is valid only on the channel and not e.g. on the contacts). Hence, the current density distributions in the patterned and unpatterned channels are obtained by taking the square root of Fig. S2(e), S2(f), and are provided in Fig. S2(g), S2(h) as well as Fig. 2(a), 2(b) of the main text. For easier quantitative visualization, the variations of (unfiltered) SThM voltage, temperature, and the computed current density are provided along the width of the device in Fig. S2(i) and S2(j) for the patterned and unpatterned device, respectively.

**Fig. S2.** Results of scanning thermal microscopy on patterned (left column) and unpatterned (right column) back-gated ITO transistors. **(a, b)** Topography, with dashed lines delineating the ITO channel area. **(c, d)** SThM voltage (normalized). A value of zero corresponds to ambient temperature (no self-heating). **(e, f)** Normalized temperature maps that result after Wiener deconvolution. **(g, h)** The square root of temperature maps, approximately proportional to current density (only in the channel). **(i, j)** Normalized SThM voltages, temperatures and current densities along the width direction (as a function of the  $y$ -coordinate) halfway between the contacts (i.e. for  $x = 0$ ), for easier quantitative comparison.

Also shown in Fig. S2(j) is the simulated current density distribution for the device geometry of Fig. S2(b), showing good agreement with that extracted from the thermal measurement. For this simulation, negligible bias parameter ( $v \ll 1$ ) was assumed, consistent with the bias point of the measured device; and negligible contact resistance and velocity saturation parameters were assumed ( $r \cong 0, s \cong 0$ ), consistent with the relatively long channel ( $L \cong 2 \mu\text{m}$ ). Note that under these conditions, the exact value of mobility merely acts as a scaling factor for current, so its exact value is irrelevant for Fig. S2(j), where the current density is normalized to a peak value of unity.

## 2. REVISITING OUR PREVIOUS EXPERIMENTAL STUDY

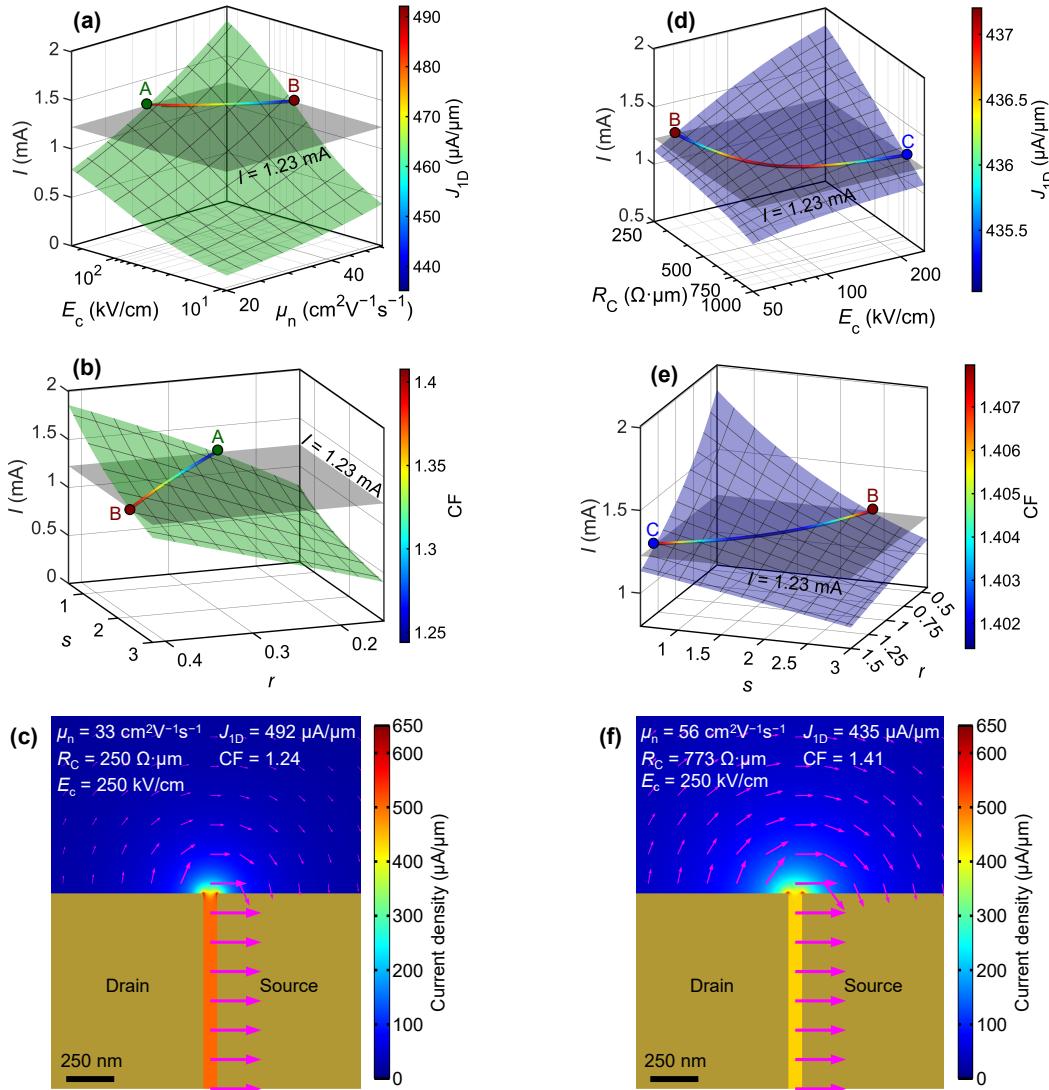

In our earlier work by Daus *et al.*,<sup>13</sup> we fabricated and characterized high-performance monolayer 2D semiconductor transistors on flexible substrates. Some devices were fabricated without patterning a channel to minimize process-induced damage to the transition metal dichalcogenide (TMD) channel. The best-performing device was an unpatterned-channel MoS<sub>2</sub> transistor with Au contacts and contact spacing of  $L = 82 \text{ nm}$  and contact width of  $W = 2 \mu\text{m}$ , with the highest current was 1.23 mA, measured at  $V_{\text{ov}} = 10 \text{ V}$  and  $V_{\text{DS}} = 1 \text{ V}$ . Given the short channel and the difficulty of achieving good contacts to TMDs (contact resistance  $R_C$  commonly on the order of  $1 - 10 \text{ k}\Omega \cdot \mu\text{m}$ ), such a device is likely to be contact-dominated. Because this contributes to current spreading (as demonstrated in Section III.B of the main text), extracting current density  $J_{\text{ID}}$  for proper benchmarking necessitated careful simulations of fringe currents with various possible values of mobility ( $\mu_n$ ) and  $R_C$ . The result of the extraction was  $J_{\text{ID}} = 466 \pm 40 \text{ }\mu\text{A}/\mu\text{m}$ . In this section, we reanalyze this device in the framework of the present work, also accounting for velocity saturation which was not considered in our previous study.

Given  $I = 1.23 \text{ mA}$ , our task is to estimate  $J_{\text{ID}}$  such that  $I = \text{CF} \times W J_{\text{ID}}$ . Because the unknown parameters  $\mu_n$ ,  $R_C$ , and saturation velocity ( $v_{\text{sat}}$ ) influence CF as well as  $J_{\text{ID}}$ , there is no unique set of parameters that yields the correct current, so the best we can do is determine the possible range of  $J_{\text{ID}}$  with reasonable bounds on  $\mu_n$ ,  $R_C$  and  $v_{\text{sat}}$ . For  $\mu_n$ , we assume an upper bound of  $56 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , which is twice as high as the highest MoS<sub>2</sub> mobility measured in our prior experimental study,<sup>13</sup> and comparable to high-quality chemical-vapor deposited (CVD) monolayer MoS<sub>2</sub>.<sup>14</sup> For  $R_C$ , we assume a lower bound of  $250 \Omega \cdot \mu\text{m}$ , comparable to the lowest values reported for monolayer CVD MoS<sub>2</sub> with Au contacts.<sup>14</sup> Finally, we assume  $v_{\text{sat}}$  lies between  $5 \times 10^5 \text{ cm/s}$  and  $5 \times 10^6 \text{ cm/s}$ , safely containing the values previously determined for CVD MoS<sub>2</sub>.<sup>15</sup> Assuming  $\mu_n > 20 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1} \text{V}$ , this implies a critical field  $E_C = v_{\text{sat}}/\mu_n$  between  $8.9 \text{ kV/cm}$  and  $250 \text{ kV/cm}$ , or equivalently, a velocity saturation parameter  $s = V_{\text{DS}}/(LE_C)$  between 0.57 and 8.

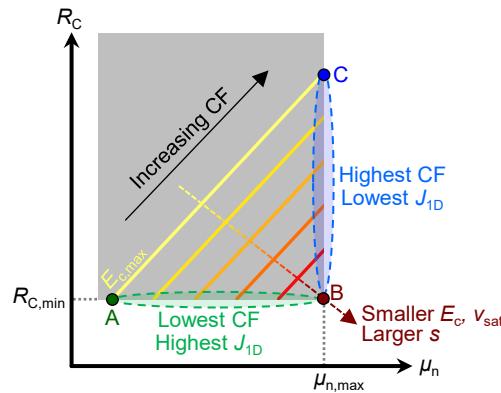

We start by recognizing that with  $v_{\text{sat}}$  kept constant, if we increase  $\mu_n$  (decreasing the channel resistance), we must simultaneously increase  $R_C$  to keep  $I$  unchanged. This is conceptually visualized in Fig. S3, where

**Fig. S3.** The space of unknown parameters  $\mu_n$ ,  $R_C$ ,  $s$  which determine  $J_{\text{ID}}$  and CF. The shaded region indicates the physically sensible range of  $\mu_n$  and  $R_C$ . Each solid line indicates the  $\mu_n$ ,  $R_C$  combination that matches the experimentally measured current  $I = 1.23 \text{ mA}$  for a fixed value of  $E_c$ , and hence  $s = V_{\text{DS}}/(LE_c)$ .

each solid line indicates the  $(\mu_n, R_C)$  combinations that yield the correct current with  $E_C$  (and hence  $s$ ) kept fixed. With increasing  $\mu_n$  and  $R_C$ , the transistor becomes more contact-limited: note that the contact resistance parameter  $r = \mu_n C_{\text{ox}} R_C V_{\text{ov}}/L$  increases. Consequently, to establish an upper bound for CF (lower bound for  $J_{\text{ID}}$ ), we must look in the upper right end of each line indicated by the blue oval where  $\mu_n = \mu_{n,\text{max}} = 56 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , and look for the lower bound for CF (upper bound for  $J_{\text{ID}}$ ) in the green oval where  $R_C = R_{C,\text{min}} = 250 \Omega \cdot \mu\text{m}$ . Therefore, to determine the possible range of  $J_{\text{ID}}$ , it suffices to evaluate it in only these two regions rather than for every allowed combination of parameters  $\mu_n, R_C, v_{\text{sat}}$ .

To find the highest  $J_{\text{ID}}$  (lowest CF), we set  $R_C = 250 \Omega \cdot \mu\text{m}$ , vary  $\mu_n$  and  $E_C$  within their respective allowed ranges, and simulate the resulting current  $I$  which includes fringe currents. The resulting  $I(\mu_n, E_C)$  surface is shown in Fig. S4(a). Its intersection with the  $I = 1.23 \text{ mA}$  plane yields the solution curve we are

**Fig. S4.** (a, d) Simulated current  $I$  as a function of (a)  $\mu_n$  and  $E_c$  with  $R_C = 250 \mu\text{A}/\mu\text{m}$ , and (b)  $R_C, E_c$  with  $\mu_n = 56 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ . The computed value of current density  $J_{\text{ID}}$  is indicated by the color of the solution curve where the simulated current matches the experimental value  $1.23 \text{ mA}$ . (b, e) The same data visualized in terms of contact resistance and velocity saturation parameters  $r$  and  $s$ , where the colors indicate CF. (c, f) Simulated current density maps for (c) parameter set A ( $\mu_n = 33 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ,  $R_C = 250 \Omega \cdot \mu\text{m}$ ,  $E_c = 250 \text{ kV/cm}$ ), and (f) parameter set C ( $\mu_n = 56 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ,  $R_C = 773 \Omega \cdot \mu\text{m}$ ,  $E_c = 250 \text{ kV/cm}$ ).

after, allowing us to determine the  $\mu_n, E_c$  pairs that yield the measured current. For each pair, we compute  $J_{1D}$  (see Section S3) and color map it onto the solution curve. The highest  $J_{1D}$  (492 mA) occurs at point  $A(\mu_n = 33 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}, R_C = 250 \Omega\cdot\mu\text{m}, E_c = 250 \text{ kV/cm})$ , labeled on Fig. S3 and Fig. S4.