# Precursor Engineering of Atomic Layer Deposition for Top-Gate Insulators on Monolayer MoS<sub>2</sub> Transistors

Alexander B. Shearer, Jung-Soo Ko, Anh Tuan Hoang, Andreas Werbrouck, Amnon Rothman, Dea Fackovic Volcanjk, Yuan-Mau Lee, Robert K. A. Bennett, Andrew J. Mannix, Krishna C. Saraswat, Eric Pop, and Stacey F. Bent\*

Cite This: *ACS Nano* 2025, 19, 33473–33484

Read Online

## ACCESS |

Metrics & More

Article Recommendations

Supporting Information

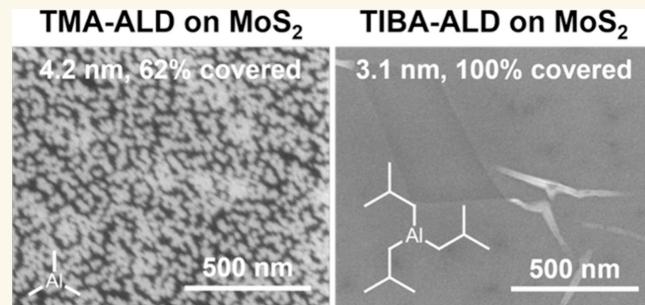

**ABSTRACT:** Integration of ultrathin, high-quality gate insulators is critical to the success of two-dimensional (2D) semiconductor transistors in next-generation nanoelectronics. Here, we investigate the impact of atomic layer deposition (ALD) precursor choice on the nucleation and growth of insulators on monolayer MoS<sub>2</sub>. Surveying a series of aluminum (AlO<sub>x</sub>) precursors, we observe that increasing the length of the ligands reduces the nucleation delay of alumina on monolayer MoS<sub>2</sub>, a phenomenon that we attribute to improved van der Waals dispersion interactions with the 2D material. Using the precursor triisobutylaluminum (TIBA), we achieve uniform coverage of ~3 nm AlO<sub>x</sub> on MoS<sub>2</sub> after just 30 cycles. We also build top-gated transistors with alumina seed layers grown by different precursors, demonstrating how the nucleation behavior of the seed layer influences the device behavior. With a bilayer stack of TIBA-AlO<sub>x</sub> and HfO<sub>2</sub> as the top-gate insulator, we achieve *n*-type MoS<sub>2</sub> transistors with negligible hysteresis, small and positive threshold voltage, ~80 mV/dec subthreshold swing at room temperature, and a top-gate equivalent oxide thickness of 0.95 nm. Through this work, we develop a simple, industry-compatible, all-ALD process for depositing a top-gate insulator directly on monolayer MoS<sub>2</sub>, and we elucidate critical insights into how the ALD chemistry can be tuned to improve insulator deposition.

**KEYWORDS:** atomic layer deposition, precursor engineering, physisorption, 2D materials, transition metal dichalcogenides, transistor

## INTRODUCTION

Scaling silicon field-effect transistors (FETs) to sub-10 nm dimensions is increasingly challenging due to short channel effects that lead to high leakage currents and excessive static power consumption. Advanced transistor architectures like FinFETs and gate-all-around (GAA) FETs can mitigate short channel effects and improve gate control, but reduction of silicon channel thickness below 3–4 nm to improve electrostatics comes with reduced mobility and performance trade-offs,<sup>1–4</sup> due to electron- (or hole-) surface scattering. To address these limitations, ultrathin two-dimensional (2D) semiconductors such as transition metal dichalcogenides (TMDCs) have emerged as promising candidates. These materials are less than 1 nm thick in single layers, offering enhanced electrostatic gate control and carrier confinement relative to three-dimensional (3D) materials due to their atomic thinness. Additionally, due to the lack of dangling bonds, they offer reduced surface scattering, providing good

mobility even in single layers.<sup>5</sup> However, to incorporate 2D semiconductors into well-behaved transistors, many processing challenges must be overcome, including the integration of the gate insulator into a gate stack.<sup>6,7</sup>

Generally, the gate insulator in modern transistors is deposited via atomic layer deposition (ALD). Widely used in the semiconductor industry, ALD is a scalable, low-temperature materials deposition technique that offers excellent conformality, a high degree of compositional control, and angstrom-level thickness control due to its self-limiting nature. However, ALD is contingent on the precursor reacting with

Received: June 26, 2025

Revised: August 21, 2025

Accepted: August 22, 2025

Published: September 8, 2025

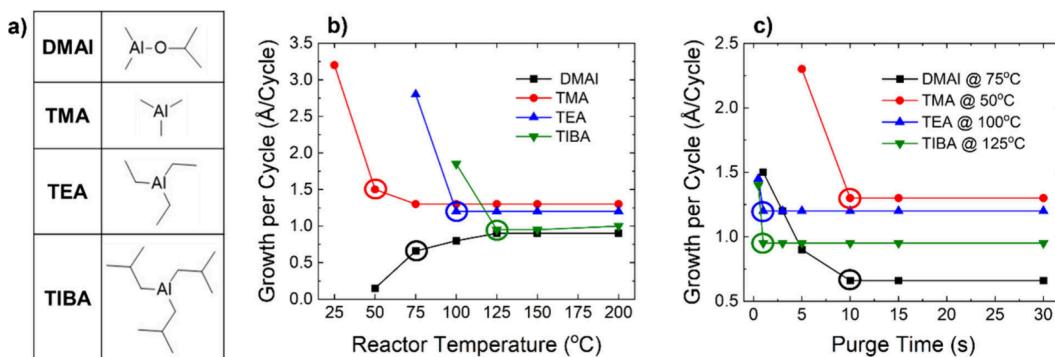

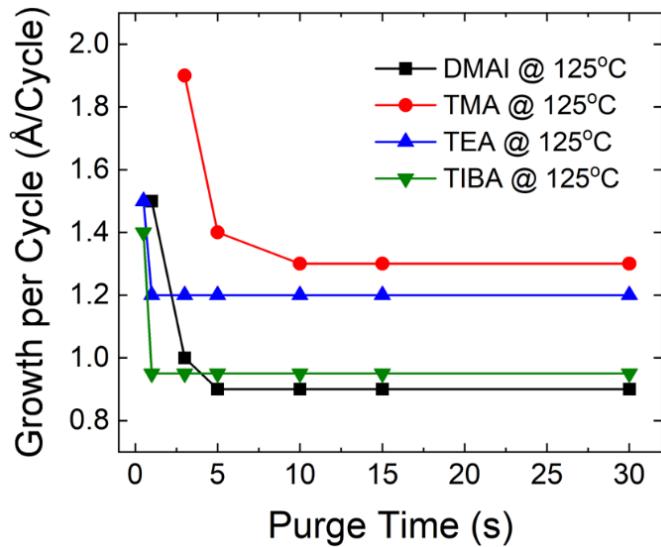

**Figure 1. Growth studies of each precursor under different ALD conditions.** (a) Skeletal formulas for each Al precursor and their acronyms. The growth per cycle (GPC) of  $\text{AlO}_x$  ALD by each precursor on  $\text{SiO}_2$  as a function of (b) reactor temperature and (c) Al precursor purge time. The processes in (b) each used an excessively long purge time (60 s) for the precursor to prevent gas-phase reactions from occurring. The circled data points in (b) indicate the lowest temperature feasible (LTf). The data in (c) were collected at the respective LTf for each precursor, as noted. The GPC was determined after 30 cycles of ALD for each precursor. The circled data points in (c) indicate the selected purge times for each process.

the surface, usually by a ligand exchange reaction.<sup>8–12</sup> Its effectiveness on 2D materials is severely limited by the lack of reactive sites on their basal planes, leading to nonuniform nucleation only at defects and grain boundaries.<sup>13–15</sup>

Various strategies have been employed to address this issue, including the use of transformed films, buffer or seed layers, surface treatments, and ALD process modifications.<sup>16–24</sup> However, these methods often possess some detrimental limitations.<sup>25</sup> Transforming films (e.g., by converting  $\text{HfSe}_2$  into  $\text{HfO}_2$ ) requires sacrificing one layer of the 2D material, limiting its application to multilayer materials and to materials whose native oxide is of both high quality and high dielectric constant (high- $\kappa$ ).<sup>16</sup> Buffer layers deposited by physical vapor deposition (PVD), like aluminum metal, may damage or dope the 2D material.<sup>17</sup> Organic seed layers made via self-assembly usually have low dielectric constant (low- $\kappa$ ) and are not always uniform.<sup>18–20</sup> Surface treatments to create reactive sites on 2D materials involve intentionally making defects or using reactive small molecule adsorbents. As such, the surface treatments can be damaging to the surface or lead to the incorporation of contaminants.<sup>21–24</sup>

One promising, industry-compatible yet underexplored approach to achieving uniform insulator deposition on 2D materials is physisorption-assisted ALD (PA-ALD). In theory, PA-ALD represents a deposition strategy that is scalable and nondamaging, can grow insulators with high- $\kappa$ , and is easily applied to a variety of 2D materials. The most common approaches to achieving PA-ALD involve lowering the ALD process temperature to induce physisorption and to stabilize the adsorbed precursors, leading to enhanced nucleation density and ultimately better film continuity.<sup>26–30</sup> However, the ALD process temperature is not the only parameter that can be leveraged to improve physisorption and nucleation. One key ALD process parameter that has been widely overlooked is the choice of the ALD precursor. To the best of our knowledge, only one report exists, experimentally demonstrating that precursor choice does impact the deposition characteristics on a 2D material.<sup>31</sup> Nevertheless, more mechanistic insight is needed in order to design ALD processes for uniform deposition of high-quality insulators on 2D materials.

In this work, we investigate the impact of ALD precursor choice on nucleation and growth via a PA-ALD process. We

survey a series of aluminum ( $\text{AlO}_x$ ) precursors of different ligand types and sizes, including dimethylaluminum isopropoxide (DMAI), trimethylaluminum (TMA), triethylaluminum (TEA), and triisobutylaluminum (TIBA), for deposition on monolayer  $\text{MoS}_2$  (Figure 1a). We observe a trend in  $\text{AlO}_x$  coverage (DMAI < TMA < TEA < TIBA) with a wide variation in the nucleation behavior: DMAI leads to negligible coverage after 30 cycles, whereas TIBA leads to uniform continuous coverage after just 30 cycles and  $\sim 3$  nm  $\text{AlO}_x$  deposited. We propose that increasing the ligand length of the Al precursor leads to improved van der Waals (vdW) dispersion interactions with the  $\text{MoS}_2$ , a longer residence time on the surface, a higher likelihood to react with the coreactant, and consequently a higher ALD nucleation rate.

Using optimized processes for the alkylaluminum precursors (TMA, TEA, and TIBA), we create  $\text{AlO}_x$  seed layers on  $\text{MoS}_2$  for the subsequent ALD of  $\text{HfO}_2$  (with higher- $\kappa$ ), which are incorporated in top-gated  $\text{MoS}_2$  transistors. We find that the nucleation behavior of the  $\text{AlO}_x$  directly impacts the performance of the devices. For instance, the TMA-based devices show high variability and high hysteresis, owing to lack of deposition uniformity and to the defectivity of the created layer. TIBA-based devices, on the other hand, show excellent electrical characteristics such as low variability, low hysteresis, and low effective oxide thickness (EOT). For our optimized top-gate stack composed of a bilayer of 2 nm  $\text{AlO}_x$  deposited using TIBA and 2 nm  $\text{HfO}_2$ , we achieve devices with subthreshold swing (SS) of  $\sim 80$  mV/dec at room temperature, almost no hysteresis, a positive threshold voltage ( $V_T$ ) between 0 and 1 V, and an EOT of 0.95 nm. Together, these device metrics represent some of the best reported data in the literature using an industry-compatible deposition technique. Ultimately, we demonstrate the viability of direct ALD of high-quality insulators on 2D semiconductors, via precursor engineering.

## RESULTS AND DISCUSSION

**Precursor-Dependent Nucleation Study.** To create  $\text{AlO}_x$  seed layers for top-gated  $\text{MoS}_2$  transistors, the ALD recipe must be optimized to maximize nucleation. Key ALD parameters to optimize for each precursor are temperature and purge time. Each precursor has its own ALD temperature window within which self-limiting, saturated reactions and

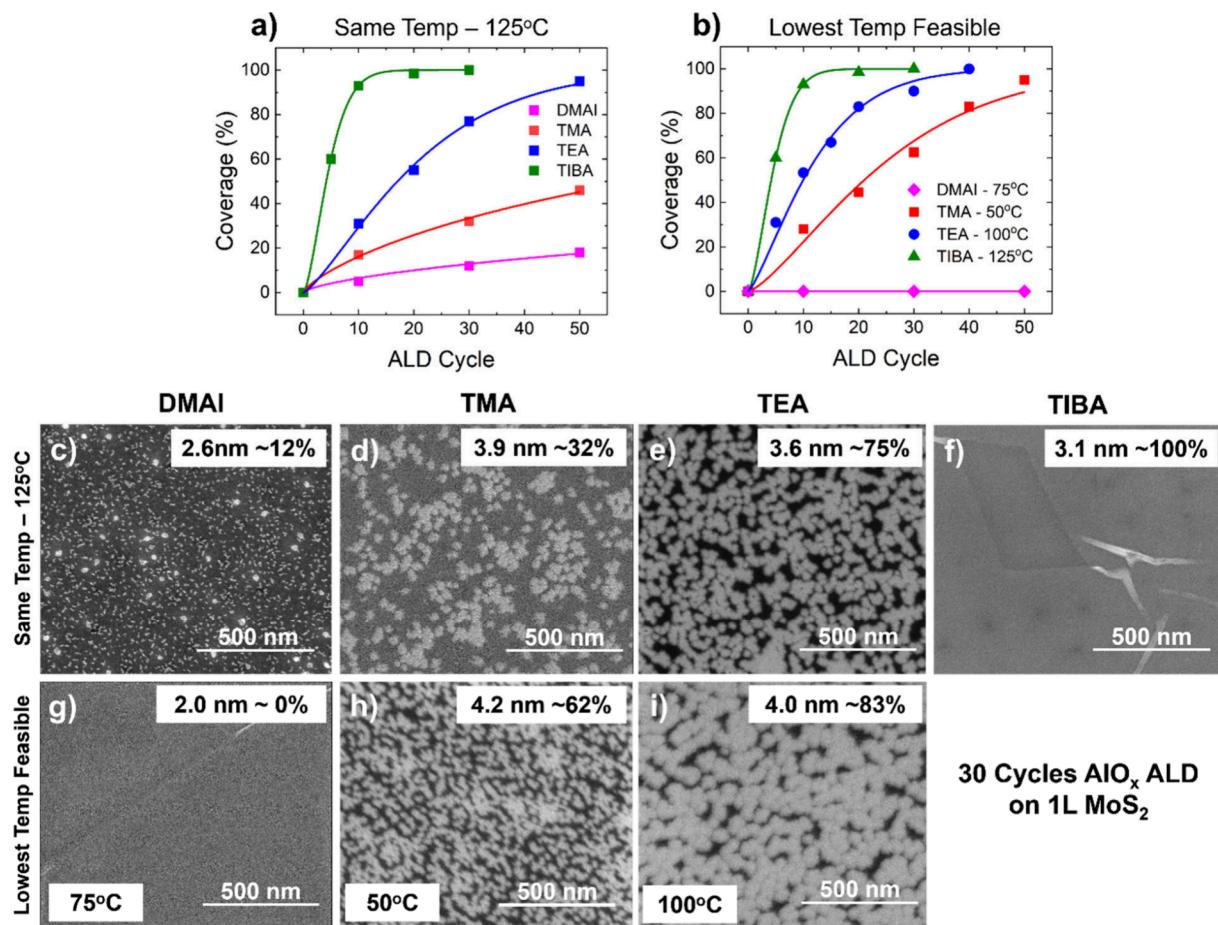

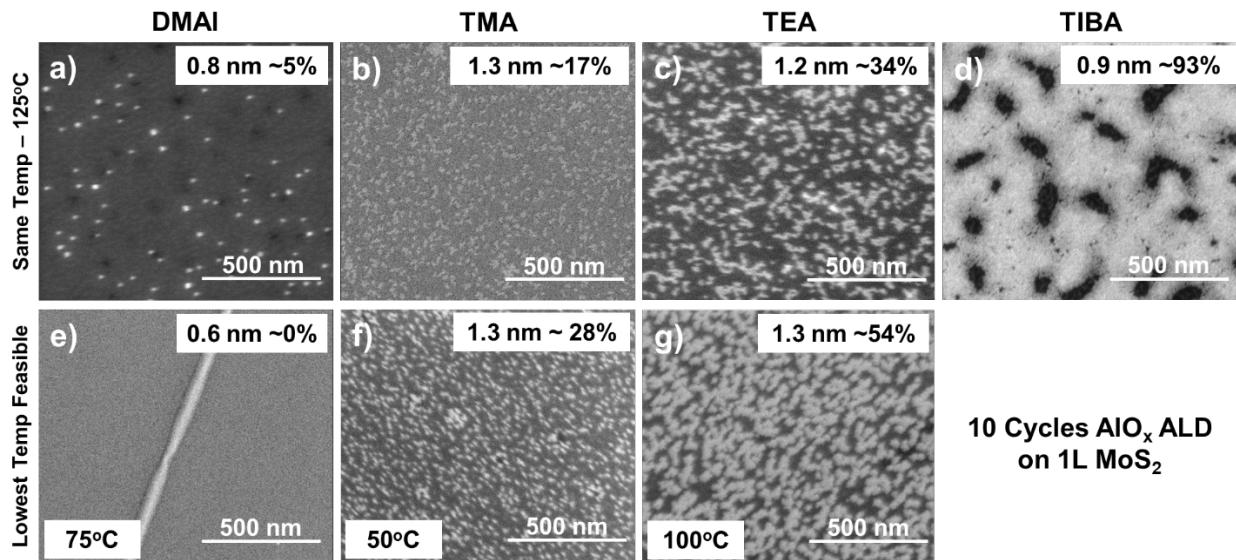

**Figure 2.** Nucleation study of each precursor on monolayer MoS<sub>2</sub>. Coverage of AlO<sub>x</sub> on MoS<sub>2</sub> as a function of ALD cycle number for each precursor at (a) the same temperature of 125 °C and (b) the LTF for each precursor. Coverage data are extracted from SEM measurements. Curves shown are fits to the data using the Avrami model.<sup>37–41</sup> Representative SEM images after 30 cycles of AlO<sub>x</sub> ALD deposited on monolayer MoS<sub>2</sub>, using (c, g) DMAI, (d, h) TMA, (e, i) TEA, and (f) TIBA as the precursor. The top row of SEM images (c–f) represents the experiments performed at 125 °C; the bottom row (g–i) represents the experiments performed at the LTF for each precursor. In the SEM images, the white/light gray regions arise from the AlO<sub>x</sub> and the darker regions derive from the monolayer MoS<sub>2</sub>. The thickness reported on each image represents the thickness measured on SiO<sub>2</sub> by spectroscopic ellipsometry (SE), i.e. the maximum thickness possible for the deposited material. The percentage shown on each SEM image represents the areal coverage of AlO<sub>x</sub> on MoS<sub>2</sub>.

well-behaved deposition can be expected. Operating outside of this window generally leads to poor growth. The poor growth can arise from slow reaction kinetics or precursor condensation at low temperature, and from thermal decomposition or precursor desorption at high temperature.<sup>11</sup> For our purposes, we seek to operate at the lower end of the temperature window in order to maximize physisorption on the 2D material, while still maintaining normal growth. Figure 1b shows the AlO<sub>x</sub> growth per cycle (GPC) on SiO<sub>2</sub> as a function of temperature for each precursor studied. It is observed that TMA, TEA, and TIBA begin to exhibit uncontrolled growth at 25 °C, 75 °C, and 100 °C, respectively, as denoted by the sudden increases in GPC. This uncontrolled growth is most likely caused by precursor condensation on the substrate. For DMAI, on the other hand, as the temperature is reduced to 50 °C the growth rate diminishes dramatically. Interestingly, for DMAI ALD at 50 °C, the deposited film is always approximately 1 nm in thickness no matter how many cycles are performed, suggesting that growth terminates once the AlO<sub>x</sub> is growing on itself rather than on the SiO<sub>2</sub> surface. This diminished growth at low temperature is most likely due to kinetic limitations. As such, for each precursor, the following

temperatures were chosen in order to maximize physisorption while still retaining controllable growth: 75 °C for DMAI, 50 °C for TMA, 100 °C for TEA, and 125 °C for TIBA. We label these values as the lowest temperature feasible (LTF) for each precursor.

The next parameter to optimize is the precursor purge time. The purge step in ALD processes is used to remove reaction byproducts and unreacted precursor from the reactor, as well as physisorbed precursor from the surface.<sup>11</sup> Here we aim to select a purge time that minimizes precursor desorption from the surface to maximize nucleation, while still adequately eliminating residual precursor from the gas phase to avoid loss of control over the deposition. The purge behavior for each precursor at the LTF is shown in Figure 1c. Additionally, the same optimization was performed for each precursor at a single temperature (125 °C) for more direct comparison of precursor nucleation behavior, and those results are shown in Supporting Information Figure S2. For each precursor, there is a sharp increase in the GPC when the purge time is too short. We attribute this GPC increase to the onset of gas phase reactions between the precursor and coreactant leading to excessive deposition on the surface and a loss of self-limiting behavior.

This phenomenon occurs for DMAI and TMA at about 5 s, and for TEA and TIBA at about 0.5 s. Consequently, the purge times selected for the optimized recipes were the following: 10 s for DMAI and TMA, and 1 s for TEA and TIBA.

Next, we compare the nucleation and coverage behavior for each precursor at both their LTF and at 125 °C. **Figure 2** provides the  $\text{AlO}_x$  coverage data for each precursor at each relevant temperature, as well as representative scanning electron microscopy (SEM) images after 30 ALD cycles. **Supporting Information Figure S3** provides additional SEM images collected after just 10 ALD cycles to show the initial nucleation stage for comparison. From **Figure 2**, we observe the following trend in  $\text{AlO}_x$  coverage: DMAI < TMA < TEA < TIBA. Although there are some differences in the coverage data at 125 °C versus LTF, the trends are the same in **Figures 2a** and **2b**.

At 125 °C (**Figure 2c–f**), the differences in surface coverage and film morphology are striking. DMAI (**Figure 2c**) results in poor nucleation (~12% coverage), with sparse, tiny, isolated nanoparticles on the surface, indicating poor surface interaction and/or slow kinetics. TMA (**Figure 2d**) shows modestly better nucleation, with numerous larger, aggregated clusters forming and slightly higher areal coverage (~45%). TEA (**Figure 2e**) exhibits denser, more uniform nucleation of small particles and partially coalesced islands, approaching continuous film formation (~75% coverage). In contrast, TIBA (**Figure 2f**) achieves nearly complete coverage (~100%) with a dense, uniform film of interconnected  $\text{AlO}_x$  domains, consistent with a rapid nucleation rate and strong surface affinity.

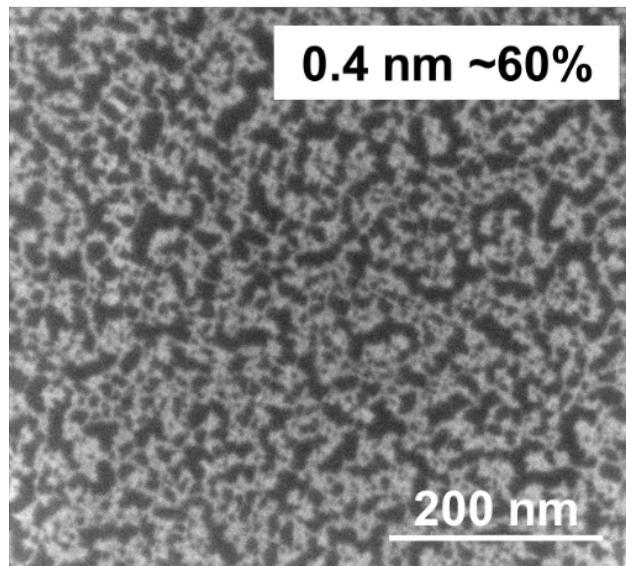

At the LTF for each precursor (**Figure 2g–i** and **2f**), we observe demonstrable changes in the nucleation behavior. For DMAI at its LTF (**Figure 2g**), there is practically 0% coverage. Despite verifying that there is  $\text{AlO}_x$  growth occurring on  $\text{SiO}_2$  at the temperature used (75 °C) on  $\text{SiO}_2$  (**Figure 1b**), there is no growth detected on the  $\text{MoS}_2$ , even at defect sites or grain boundaries, further indicating physisorption and/or kinetic issues with the precursor. On the other hand, we do observe that reducing temperature improves nucleation for the alkyl precursors. TMA (**Figure 2g**) shows significantly higher coverage (~62%), smaller, more uniform particles, and partial coalescence of the islands compared to 125 °C, indicating enhanced physisorption at lower temperatures. TEA (**Figure 2h**) also achieves improved nucleation, yielding a more continuous morphology compared to its 125 °C counterpart (~83% coverage). Nevertheless, despite the improvements in nucleation at reduced temperatures for TMA and TEA, they still do not provide the degree of uniformity and coverage that TIBA provides (**Figure 2f**), even at the higher deposition temperature. Even after just 10 cycles of ALD, equivalent to 0.9 nm  $\text{AlO}_x$  on  $\text{SiO}_2$  (**Figure S3**), the  $\text{AlO}_x$  deposited on  $\text{MoS}_2$  by TIBA shows higher coverage (~93%) than that of TMA or TEA at 30 cycles, and it results in the formation of interconnected  $\text{AlO}_x$  domains—further indicating the rapid, uniform, and dense nucleation provided by the TIBA precursor.

To better understand the nucleation behavior of  $\text{AlO}_x$  on  $\text{MoS}_2$ , we can fit the coverage data in **Figure 2a** and **2b** using the Avrami model, otherwise known as the Johnson-Mehl-Avrami-Kolmogorov (JMAK) model.<sup>37–41</sup> The model describes isothermal nucleation and phase change as a function of time, and it can be readily adapted to describe ALD phenomena,<sup>42–44</sup> as

$$f_\beta = 1 - \exp(-k \cdot t^n) \quad (1)$$

where  $f_\beta$  is the transformed area (i.e., covered area),  $k$  is a constant,  $n$  is the Avrami exponent, and  $t$  is the growth time which correlates with ALD cycle number.<sup>37,39,40,42,44,45</sup> The Avrami exponent provides information regarding the nucleation and growth behavior. Generally, an Avrami exponent of  $n = 2$  suggests instantaneous, uniform nucleation followed by linear or parabolic growth and a rapid coalescence of islands. An Avrami exponent of  $n = 1$  suggests constant nucleation throughout the deposition process. An Avrami exponent of  $n < 1$  suggests the growth is severely inhibited, and it is initiated nonuniformly at defects or heterogeneous nucleation sites. It can also suggest nonclassical growth mechanisms such as fractal growth or diffusion-limited aggregation. Fitting the experimental coverage data, we acquire the fits shown in **Figure 2**, and the Avrami exponent values found in **Table 1**.

**Table 1. Avrami Exponent Values at the Same Temperature (125 °C) and at the LTF for Each Precursor**

|      | <i>n</i> at 125 °C | <i>n</i> at LTF |

|------|--------------------|-----------------|

| DMAI | 0.66               | N/A             |

| TMA  | 0.76               | 1.06            |

| TEA  | 1.29               | 1.33            |

| TIBA | 1.53               | 1.53            |

The results show that TIBA possesses an  $n \approx 1.5$ . This value suggests a mixture of instantaneous nucleation and continuous nucleation as the process continues and as the film coalesces. In other words, the early stage of the process should lead to fairly uniform and high coverage of the  $\text{MoS}_2$ , as supported by the SEM image in **Supporting Information Figure S4** taken after 5 ALD cycles. During the remainder of the ALD process, the gaps in the mesh-like network coalesce via growth and continued nucleation, leading to rapid convergence of the film. At 125 °C, TEA has a slightly lower  $n \approx 1.3$ , suggesting that it undergoes less instantaneous nucleation, and its coverage is more contingent on constant nucleation. Consequently, nucleation and growth are slower relative to TIBA, leading to a longer coalescence time (50 cycles for TEA, 30 cycles for TIBA). At the LTF for TEA, there is not a significant change in the  $n$  value, most likely due to the similarity in temperatures (100 °C versus 125 °C).

For TMA and DMAI at 125 °C the  $n$  values are below 1, suggesting that nucleation is severely inhibited. In other words, little of the physisorption and subsequent reaction that is needed to promote uniform nucleation is occurring. Rather, nucleation likely begins only at heterogeneous nucleation sites, like defects on the  $\text{MoS}_2$  surface,<sup>13–15</sup> and it does not persist throughout the ALD process. When operating at the LTF for TMA,  $n$  increases to  $\sim 1$ . This increase suggests that going to lower temperature results in more continuous nucleation, probably afforded by improvements in physisorption at the lower temperature. Overall, we observe that TIBA possesses a high instantaneous nucleation rate, as well as a high constant nucleation rate, while the other precursors have much lower nucleation rates. Consistent with a physisorption-enhanced nucleation mechanism, reducing the temperature does improve the nucleation rate for TMA and TEA.

We hypothesize that DMAI fails to produce  $\text{AlO}_x$  coverage for several reasons. First, the DMAI precursor is known to dimerize under ALD conditions.<sup>46</sup> Upon dimerization, each Al

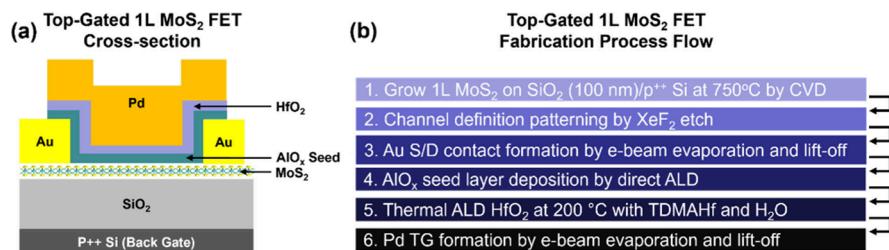

Figure 3. (a) Schematic cross-section (not to scale) of a monolayer (1L) MoS<sub>2</sub> transistor with a Pd top-gate (TG) and the highly doped Si back-gate (BG). (b) Its corresponding fabrication process flow. Electrical measurements are all performed at room temperature after annealing in vacuum at 150 °C to remove surface moisture. Channel length (source to drain spacing) is 3  $\mu$ m for all devices in this study.

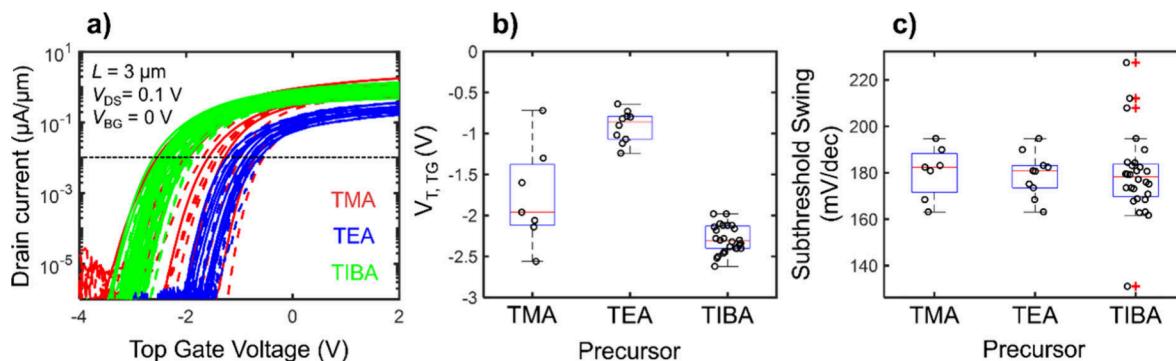

Figure 4. Electrical measurements of our 1L MoS<sub>2</sub> transistors. The top-gate insulator stack is a bilayer composed of 6 nm HfO<sub>2</sub> grown by ALD on top of a 3 nm ALD AlO<sub>x</sub> seed layer, which is on the MoS<sub>2</sub> channel. (3 nm corresponds to the AlO<sub>x</sub> thickness on a witness SiO<sub>2</sub> substrate.) The seed layer was grown by direct ALD using either TMA (red), TEA, (blue), or TIBA (green). (a) Measured  $I_D$  vs  $V_{TG}$  for devices with AlO<sub>x</sub> seed layers grown by the different precursors. Solid and dashed lines represent forward and reverse sweeps, respectively.<sup>55</sup> Sweeps of numerous devices are shown for each precursor (7 for TMA, 10 for TEA, and 24 for TIBA). Corresponding box plots of (b)  $V_{T,TG}$  (extracted at 10 nA/ $\mu$ m) and (c) subthreshold swing for each AlO<sub>x</sub> seed layer. In (c) the red + symbols represent statistical outliers.

metal center becomes bound to two oxygens. These Al–O bonds significantly reduce the reactivity of the precursor by diminishing the driving force for oxidation of the metal center by the coreactant. Additionally, dimerization leads to increased steric bulk around the Al metal center, which hinders interaction with the coreactant, further reducing the reactivity of the precursor.<sup>47,48</sup> Therefore, the kinetics of DMAI are relatively poor. We attribute the lack of physisorption-enhanced nucleation at low temperature to these kinetic limitations. Furthermore, in its dimeric form, DMAI is no longer trigonal planar in its molecular geometry. Rather, the Al center becomes tetrahedrally coordinated. This conformation possesses three-dimensional steric bulk that disrupts planar contact with the MoS<sub>2</sub> surface. The resulting reduction in contact area between the precursor and the MoS<sub>2</sub> likely weakens vdW interactions, reducing the physisorption affinity of the precursor.<sup>47,48</sup> As such, it is likely that neither the physisorption of DMAI nor its reaction kinetics are conducive for nucleation on an inert TMDC surface.

While the geometry of DMAI may not be conducive for good vdW interactions with the MoS<sub>2</sub> surface, the aluminum alkyl precursors remain in their monomeric, trigonal planar conformation under ALD conditions.<sup>46</sup> This conformation enables the precursor and its ligands to lie relatively flat against the MoS<sub>2</sub> basal plane. Thus, they possess a more ideal geometry for establishing vdW interactions with the TMDC and for physisorption. Additionally, the aluminum alkyls are highly reactive, providing good kinetics for nucleation.<sup>8–11,46</sup> In fact, the only disparity between TMA, TEA and TIBA is their ligand length, and we observe a direct correlation between ligand length and AlO<sub>x</sub> coverage on the TMDC. We

propose that the longer ligands lead to improved vdW dispersion interactions with the TMDC, leading to an increased residence time on the surface. This proposal was recently corroborated by a recent theoretical study on the stability of Al precursors adsorbed on the MoS<sub>2</sub> surface.<sup>49</sup> This increased residence time, in turn, generates a higher probability of reaction with the coreactant and a higher nucleation rate. Therefore, in the comparison of precursors at the same temperature, we posit that it is the difference in physisorption that leads to the exceptional coverage provided by TIBA relative to the others.

By lowering the temperature of deposition for the other precursors (to 50 °C for TMA and to 100 °C for TEA), the weaker physisorption of TMA and TEA relative to that of TIBA can be compensated for by the reduced thermal energy, allowing better physisorption. That increase in physisorption can in turn improve the nucleation during ALD. Nevertheless, at their respective LTFs, TMA and TEA still do not provide comparable coverage to TIBA. We posit that although the physisorption step of nucleation is improved by going to lower temperature, the kinetics of subsequent reaction steps is worsened. We thus conclude that by providing better vdW dispersion interactions and better physisorption, precursors with longer ligands (like TIBA) permit the ALD process to be operated at higher temperatures, thereby also improving the kinetics of nucleation. Ultimately, there is a delicate balance between operating at a temperature that leads to a high degree of precursor physisorption – the first step of nucleation on 2D materials – and operating at a temperature that promotes reaction with the coreactant – the second step of nucleation.

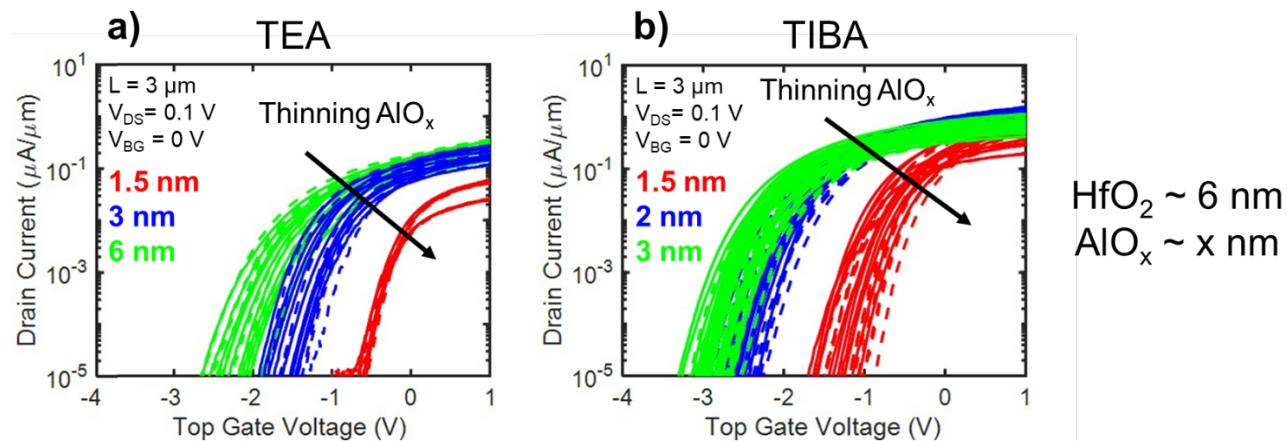

**MoS<sub>2</sub> Device Characterization.** To study the impact of precursor choice and nucleation behavior on TMDC device performance, we deposit AlO<sub>x</sub> on MoS<sub>2</sub> to fabricate top-gated monolayer (1L) MoS<sub>2</sub> transistors. The AlO<sub>x</sub> deposited on MoS<sub>2</sub> serves as a seed layer for high- $\kappa$  HfO<sub>2</sub> thermal ALD, thereby forming bilayer insulator stacks. The device cross-section diagram and the fabrication process scheme are shown in Figure 3. We first fabricate devices using AlO<sub>x</sub> seed layers of 3 nm equivalent thickness grown by TMA, TEA, and TIBA using recipes optimized for maximizing coverage (Table 3), and we evaluate their electrical characteristics. Corresponding drain current ( $I_D$ ) vs top-gate voltage ( $V_{TG}$ ) curves, the extracted threshold voltages ( $V_{T,TG}$ ), and extracted subthreshold swings (SS) are shown in Figure 4. We observe that devices with TMA-based seed layers (Figure 4a – red) show relatively high hysteresis ( $\sim$ 160–400 mV at 10 nA/ $\mu$ m). Additionally, they show substantial device-to-device variation in the threshold voltage ( $\Delta V_{T,TG} \approx 1.8$  V), summarized in Figure 4b. The devices with TEA- and TIBA-based seed layers, on the other hand, show negligible hysteresis ( $<10$  mV) and much lower device-to-device variation in the threshold voltage ( $\Delta V_{T,TG} \approx 0.6$  V for TEA and  $\Delta V_{T,TG} \approx 0.7$  V for TIBA). We attribute the improvements in hysteresis and device-to-device variation, for TEA and TIBA devices vs TMA devices, to the enhanced nucleation properties of the seed layer, leading to more uniform and less defective top-gate insulator stacks.

Interestingly, the minimum subthreshold swing (Figure 4c) is similar for all devices using ALD AlO<sub>x</sub> seed layers (SS  $\approx$  180 mV/dec at room temperature), suggesting the interface trap density is similar across all AlO<sub>x</sub>/MoS<sub>2</sub> interfaces. However, there is a notable difference between the top-gate threshold voltage of the TEA- and TIBA-based devices ( $V_{T,TG} \approx -0.9$  V for TEA and  $V_{T,TG} \approx -2.4$  V for TIBA). This disparity could arise due to differences in stoichiometry and density between the two AlO<sub>x</sub> seed layers leading to variations in the amount of fixed charge within the insulator (Supporting Information Figure S1 and Discussion 1). It could also arise due to differences in the thickness<sup>7,51,52</sup> or morphology of the AlO<sub>x</sub> seed layers on the MoS<sub>2</sub>, which would affect the amount of fixed charge present at the insulator/MoS<sub>2</sub> interface. Despite our best attempts to grow the same thickness of AlO<sub>x</sub> for the seed layers for fair comparison, the difference in nucleation behaviors for the TEA and TIBA precursors can lead to slightly varied nucleation delays, with that of TEA being longer than that of TIBA. Thus, it may be expected that the TEA AlO<sub>x</sub> seed layer is slightly thinner and slightly less smooth than that of the TIBA layer. The difference in thickness could lead to less fixed charge and a more positive threshold voltage.<sup>7,50,51</sup> The difference in surface roughness could also alter the interface between the AlO<sub>x</sub> and HfO<sub>2</sub>, leading to the formation of interface dipoles that could similarly shift the threshold voltage.<sup>7,52–54</sup> More systematic experimentation would be required to ascertain the specific mechanism by which the  $V_T$  is shifted; however, these results suggest that the  $V_T$  can be engineered through careful tuning of the seed layer properties.

We note that the AlO<sub>x</sub> seed layer thickness of 3 nm does not correspond to full coverage for either TMA or TEA according to our nucleation studies (Figure 2); only TIBA reaches full coverage after 3 nm of material is deposited. Nevertheless, we measure excellent device performance for the TEA-based seed layer, and we observe that the TMA-based devices – despite their hysteresis and device-to-device variation – do operate as transistors, with on/off ratios of about 10<sup>6</sup>, indicating that the

devices are not shorting through the gate and the insulator is continuous. We provide one potential explanation for this unexpected performance. We speculate that as a result of the device fabrication process itself, there may be contaminants on the surface of the MoS<sub>2</sub> channels used for devices that were not present on the MoS<sub>2</sub> samples used for ALD characterization by SEM.<sup>22,56–58</sup> Such contaminants, such as photoresist polymer residues, could act as nucleation sites and promoters for seeding AlO<sub>x</sub> growth, leading to more deposition than was observed on the more pristine samples (e.g., Figure 2). Nevertheless, the data show a demonstrably significant difference in the performance of the devices fabricated using seed layers grown by different ALD precursors indicating that any effect of contamination must be relatively minor. Clearly, the precursor chosen for the seed layer deposition has a large impact and ultimately dictates the device performance (vide infra).

After confirming operational top-gated MoS<sub>2</sub> transistor devices, we next reduce the insulator stack thickness to increase the top-gate insulator capacitance. We focus first on thinning down the AlO<sub>x</sub> seed layer, since AlO<sub>x</sub> ( $\kappa \sim 6$ –8) has a lower dielectric constant than HfO<sub>2</sub> ( $\kappa \sim 15$ –20).<sup>59</sup> The results of thinning down the seed layer grown by TEA and TIBA are shown as  $I_D$  vs  $V_{TG}$  curves in Supporting Information Figure S5. First, we observe a positive shift in the threshold voltage as the AlO<sub>x</sub> layer is thinned for both TEA and TIBA. We attribute this shift to a combination of phenomena, including but not limited to (1) a reduction in the amount of fixed charge present in the overall gate insulator stack as the AlO<sub>x</sub> layer is thinned,<sup>7,50,51,60–65</sup> (2) a change in the dipole strength at the HfO<sub>2</sub>/AlO<sub>x</sub> interface,<sup>7,52–54</sup> and/or (3) the change in proximity between either the HfO<sub>2</sub>/AlO<sub>x</sub> or Pd/HfO<sub>2</sub> interface dipoles to the channel and the subsequent coupling.<sup>66–68</sup> Nonetheless, it is difficult to conclude the specific mechanism by which this shift is occurring. Previous studies show that ALD AlO<sub>x</sub> can carry either negative fixed charge (from O interstitials and Al vacancies)<sup>7,50,51,60</sup> or positive fixed charge (from dangling bonds, ligand byproducts, and  $-\text{OH}/-\text{H}$  groups),<sup>51,61,62</sup> and that HfO<sub>2</sub> likewise can be positively<sup>63,64</sup> or negatively<sup>65</sup> charged depending on defect complexes and impurities. Combining those charge effects with effects relating to potential interfacial dipoles and the proximity of those dipoles to the channel makes deduction of mechanistic insight into the observed  $V_T$  shift particularly difficult. More mechanistic experimentation would be required for a definitive conclusion. Nevertheless, a key result of this study is that the  $V_T$  can be engineered through careful tuning of the seed layer by either its thickness, morphology, or stoichiometry.

Most importantly, we observe in these experiments (see Supporting Information Figure S5) that the TEA-based AlO<sub>x</sub> layer cannot be thinned down below 3 nm without enduring significant losses in device yield. Upon extreme reduction in thickness, the TEA-based seed layer is likely discontinuous due to insufficient nucleation and coverage, leading to shorting through the gate stack and poor device yield. The TIBA-based AlO<sub>x</sub> seed layers, on the other hand, can be thinned to 1.5 nm and still provide excellent device yield and performance. We attribute the improved yield, once again, to improvements in the nucleation behavior which leads to a continuous, uniform, dense film sooner in the growth process, thereby allowing the insulator seed layer to be functional even when it is only 1.5

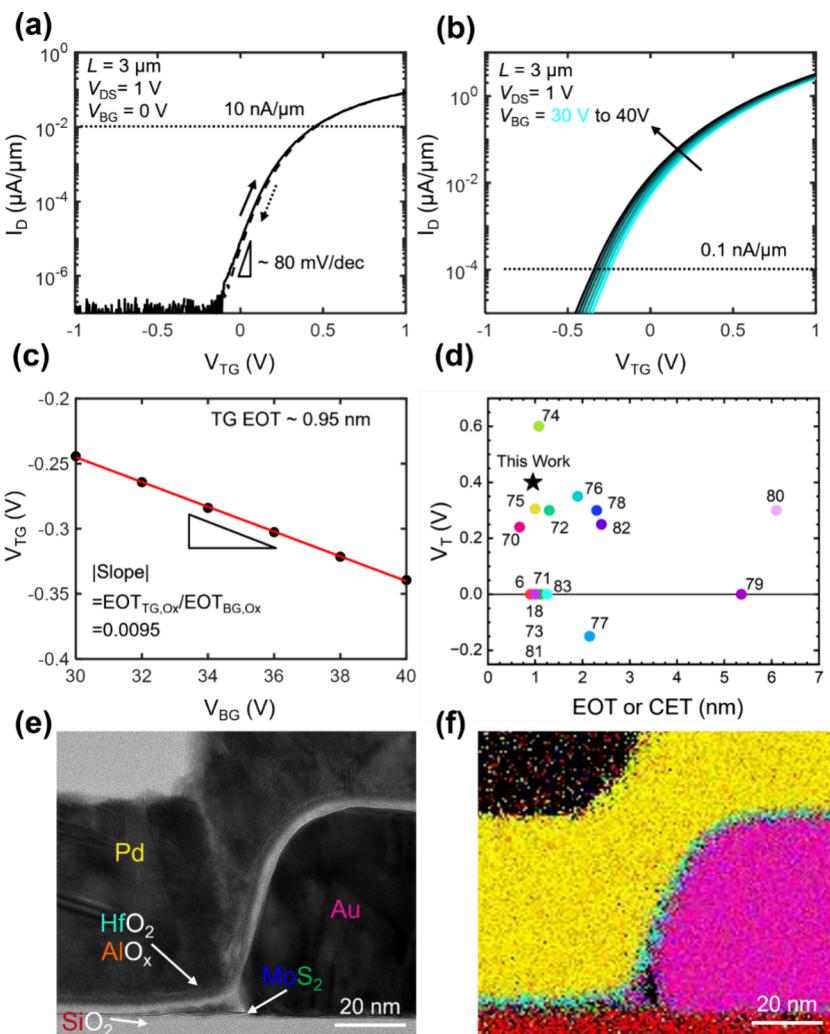

**Figure 5.** Hero device characteristics for the 1L  $\text{MoS}_2$  transistor with the best insulator bilayer stack composed of 2 nm  $\text{HfO}_2$  on a 2 nm  $\text{AlO}_x$  seed layer grown by direct ALD using TIBA as the precursor. (a) Measured  $I_D$  vs  $V_{TG}$  for the 1L  $\text{MoS}_2$  FET. Solid and dashed lines represent forward and reverse sweeps, respectively. (b) Measured  $I_D$  vs  $V_{TG}$  using a wide  $V_{BG}$  range from 30 V (cyan) to 40 V (black), with 2 V step. Horizontal dashed line at 0.1 nA/ $\mu\text{m}$  represents the constant current value taken for extracting  $V_{T,TG}$ . (c) Extracted  $V_{T,TG}$  vs  $V_{BG}$ , representing the ratio of the top-gate EOT to the back-gate EOT. Because the back-gate EOT is known (100 nm), this provides an estimate of our top-gate EOT  $\approx 0.95$  nm. (d) Benchmarking plot of threshold voltage vs EOT or CET (capacitance equivalent thickness) reported for top-gated  $\text{MoS}_2$  transistor devices in literature that exhibited minimal hysteresis.<sup>6,18,70–83</sup> (e) Cross-sectional TEM image of the hero device and (f) the corresponding EDS mapping.

nm thick. This property represents a significant advantage compared to the other Al precursors studied.

Upon determining that TIBA can provide the thinnest interfacial seed layers, we use this precursor to fabricate an even thinner insulator stack in the transistor. We fabricate devices with a bilayer gate insulator stack composed of an ultrathin TIBA-based  $\text{AlO}_x$  seed layer ( $\sim 2$  nm) and an ultrathin  $\text{HfO}_2$  top layer ( $\sim 2$  nm). The electrical characteristics for the hero device are shown in Figure 5. This figure also shows the cross-sectional transmission electron microscopy (TEM) and energy dispersive X-ray spectroscopy (EDS) images of the hero device, as well as a benchmark plot of its performance with respect to EOT and threshold voltage. The hero device demonstrates excellent electrical performance. The device (Figure 5a) shows a decent on/off ratio ( $>10^6$ ), low hysteresis ( $<10$  mV), low subthreshold swing ( $\sim 80$  mV/dec), and a positive  $V_{T,TG}$  between 0 and 1 V ( $\sim 0.4$  V). The low hysteresis and low subthreshold swing suggest that the metal oxide has low bulk and interfacial trap and defect densities.<sup>69</sup>

The low SS is also partly attributed to increased capacitance due to insulator thinning.<sup>70</sup> The positive shift of the threshold voltage, relative to that of previous devices (Figure 4), is again attributed to reductions in the amount of fixed charge present in the insulator due to metal oxide thinning and to the increased TG insulator capacitance.<sup>60</sup> The small yet positive threshold voltage is also critical, yet historically difficult to achieve, because it guarantees the devices will be normally off at zero gate voltage. The good, positive  $V_{T,TG}$  and good on/off ratio together suggest that the device has a high quality insulator layer and the gate stack provides excellent electrostatic controllability of the 2D TMDC layer.<sup>70</sup>

The top-gate EOT cannot be accurately extracted from capacitance–voltage (C–V) measurements directly on the monolayer  $\text{MoS}_2$  devices, because their channel surface area is too small. Thus, we used an indirect estimation method that is widely used, relying on a capacitive divider between the top-gate (TG) and back gate (BG).<sup>6,7,70–73,84</sup> When measuring  $I_D$  vs  $V_{TG}$  from a transistor at various  $V_{BG}$ , the magnitude of the

slope in the corresponding  $V_{T,TG}$  vs  $V_{BG}$  represents the ratio of the top-gate EOT to back-gate EOT. Here,  $V_{T,TG}$  refers to the top-gate threshold voltage, taken at  $I_D = 10 \text{ nA}/\mu\text{m}$ . Because our samples have a back-gate insulator of 100 nm  $\text{SiO}_2$  (i.e., back-gate EOT = 100 nm), we can estimate the top-gate EOT once the ratio of the EOTs is known. Using this EOT extraction method we determine that the top-gate EOT  $\approx 0.95 \text{ nm}$  for the hero device (Figure 5b and 5c). Additionally, using the cross-sectional TEM and EDS images (Figure 5e and 5f), we determine that the insulator is approximately 4.5 nm in physical thickness, as predicted. Together, the physical thickness and the EOT suggest that the overall dielectric constant of the bilayer is  $\kappa \approx 18.5$ . According to our benchmarking (Figure 5d), these results represent some of the best in literature for top-gated  $\text{MoS}_2$  transistor devices, particularly in terms of EOT and threshold voltage, as well as subthreshold swing—three key parameters for evaluating insulator quality (EOT and SS) and gate controllability ( $V_T$ )—facilitated by a simple, industry-compatible, all-ALD process. Combining the small yet positive top-gate threshold voltage, low EOT, high on/off ratio, low SS, and low hysteresis, these devices show promise for use in low-power 2D semiconductor device applications.

## CONCLUSION

We have demonstrated the importance of precursor selection in facilitating physisorption-assisted direct ALD onto a 2D material such as  $\text{MoS}_2$ . We show that precursors with a planar geometry, high reactivity, and long ligands facilitate more physisorption on the 2D material and more reaction with the coreactant, leading to better nucleation and coverage of the 2D material. While this study focuses on  $\text{MoS}_2$ , we expect that the observed trends in precursor-dependent nucleation – particularly the role of ligand length and physisorption and precursor reaction kinetics – extend to other TMDCs with similarly inert basal planes, though material-specific variations in surface chemistry, lattice structure, and defect density may influence the exact behavior. As such, more work needs to be done exploring physisorption-assisted ALD on 2D materials. We also show in this work that the nucleation behavior of the insulator directly impacts the performance of top-gated TMDC transistors. Better nucleation behavior allows for (1) extreme thinning of the insulator and for (2) the creation of a low defectivity insulator. These properties enable top-gated TMDC transistors with subnanometer EOT, low SS, and low hysteresis. The small yet positive threshold voltage is also important and often hard to achieve with  $n$ -type TMDC transistors, ensuring they are well-behaved, enhancement-mode, i.e. normally off at zero gate voltage. Ultimately, we demonstrate the importance of ALD chemistry and its impact on device performance, and we provide insights into designing simple, industry-compatible fabrication processes for high-quality gate insulator on TMDC transistor devices, which has historically been a challenge toward integrating these materials into devices.

## EXPERIMENTAL SECTION

Si (100) wafers with a native oxide of  $\sim 1.5 \text{ nm}$  thick (WRS Materials) were used as blanket  $\text{SiO}_2$  substrates for ALD studies. We synthesized monolayer (1L)  $\text{MoS}_2$  by chemical vapor deposition (CVD) at  $750^\circ\text{C}$  from solid S and  $\text{MoO}_3$  precursors with the aid of perylene-3,4,9,10-tetracarboxylic acid tetrapotassium salt (PTAS) on 100 nm  $\text{SiO}_2$  on Si ( $\text{p}^{++}$ ) substrates.<sup>32</sup> These monolayer  $\text{MoS}_2$  samples were

used for both nucleation studies and device fabrication, wherein the Si ( $\text{p}^{++}$ ) served as a back gate, and the 100 nm  $\text{SiO}_2$  was the back gate insulator. All samples were cleaned with isopropanol and acetone, and dried by  $\text{N}_2$  prior to nucleation studies.

For  $\text{AlO}_x$  growth tests and nucleation studies, a GemStar 6 ALD reactor (Aarradiance Inc.) was used.  $\text{AlO}_x$  was grown by ALD using DMAI (Strem Chemicals, 98%), TMA (Sigma-Aldrich, 97%), TEA (Sigma-Aldrich, 93%), or TIBA (Oakwood Chemical, 95%) Al-precursors and deionized  $\text{H}_2\text{O}$  as the coreactant. Each precursor was kept in a stainless-steel bubbler. The process conditions for each precursor can be found below in Table 2. Each precursor was

**Table 2. ALD Process Conditions for Each Precursor Studied as well as for the  $\text{H}_2\text{O}$  Coreactant<sup>a</sup>**

| Precursor            | Bubbler Temperature (°C) | Pulse Time (ms) | Vapor Pressure (mTorr) |

|----------------------|--------------------------|-----------------|------------------------|

| DMAI                 | 60                       | 30              | 78                     |

| TMA                  | 25                       | 30              | 95                     |

| TEA                  | 65                       | 150             | 62                     |

| TIBA                 | 45                       | 150             | 89                     |

| Coreactant           | /                        | /               | /                      |

| $\text{H}_2\text{O}$ | 25                       | 30              | 150                    |

<sup>a</sup>For each precursor, the purge time was  $\sim 60 \text{ s}$ , unless otherwise stated.

introduced to the reactor with an  $\text{N}_2$  flow rate of 5 sccm. Precursor pulse times were selected so that exposures were similar between all precursors to allow for a fair comparison; in each case, the exposure used led to saturated growth on the  $\text{SiO}_2$  substrates. Finally, for each ALD process used, the purge time for the coreactant—in this case, water—was kept constant at an excessively long ( $\sim 60 \text{ s}$ ) value between each process to ensure that any physisorbed water desorbed before the incoming precursor pulse. This excessive coreactant purge ensured that all nucleation on the TMDC surface was due exclusively to the precursor physisorption rather than water adsorption or condensation at the various temperatures tested – enabling fair comparison of the nucleation properties of each precursor.

Spectroscopic ellipsometry (SE) (alpha-SE ellipsometer by J.A. Woollam Co.) was performed to monitor the  $\text{AlO}_x$  film thickness on  $\text{SiO}_2$  after ALD. All thicknesses reported in this work, except those from cross-sectional transmission electron microscopy (TEM), were derived from SE measurements on  $\text{SiO}_2$  because we were unable to measure the  $\text{AlO}_x$  thickness on  $\text{MoS}_2$  due to the incomplete coverage of the underlying substrate by the  $\text{MoS}_2$ . Based on previous work, we assume that there is no nucleation delay on  $\text{SiO}_2$ ,<sup>33,34</sup> whereas on  $\text{MoS}_2$ , each precursor will likely have some degree of nucleation delay, an effect which will be accentuated for more poorly performing precursors. As a result, the thicknesses reported for  $\text{AlO}_x$  grown on  $\text{MoS}_2$ , which were measured by SE on  $\text{SiO}_2$ , will represent the maximum possible thickness rather than the actual thickness.

SEM imaging was performed using an FEI Magellan 400 XHR scanning electron microscope with a field emission gun source. SEM was used to investigate the surface coverage and morphology of the  $\text{AlO}_x$  grown on  $\text{MoS}_2$  for nucleation studies. Coverage measurements were made using ImageJ software.<sup>35</sup> Cross-sectional TEM was performed to investigate the interfaces and to measure the real thicknesses of the insulator layers in the bilayer gate insulator stack in one of our better fabricated devices.

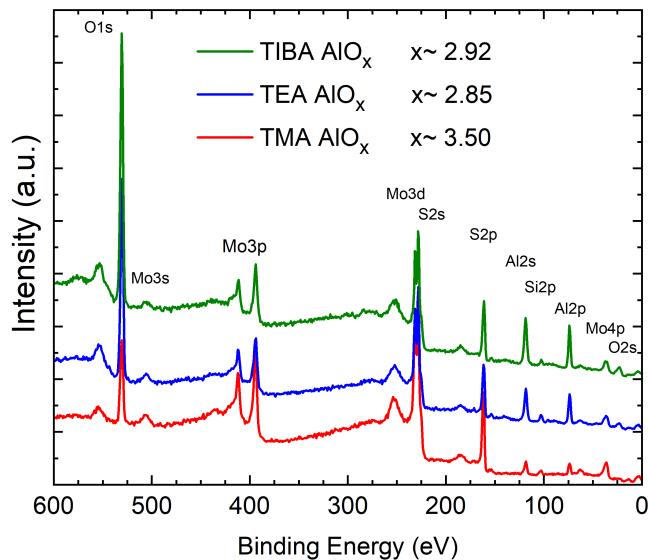

X-ray photoelectron spectroscopy (XPS) was performed using a PHI Versaprobe 3 with an  $\text{Al K}\alpha$  source radiation of 1486.6 eV to investigate the stoichiometry of the  $\text{AlO}_x$  deposited. Prior to XPS, gas-cluster ion beam (GCIB) sputtering was used for 1 min to remove adventitious carbon from the surface. Using XPS, we determined that all films grown with the aluminum precursors at the lower temperatures used in this study are nonstoichiometric, as shown in Supporting Information Figure S1. As such, we refer to the films as  $\text{AlO}_x$  rather than  $\text{Al}_2\text{O}_3$ . More discussion on the stoichiometry of the films can be found in the Supporting Information (SI Discussion 1).

For transistor fabrication, we started with the CVD-grown 1L MoS<sub>2</sub> on 100 nm SiO<sub>2</sub>/Si (p<sup>++</sup>) substrates. We patterned and etched the active channel region using a XeF<sub>2</sub> dry-etch recipe, followed by source (S) and drain (D) contact metal deposition using electron-beam evaporation of Au for MoS<sub>2</sub>.<sup>36</sup> These structures served as back-gated (BG) 1L TMDC transistors. We then deposited the AlO<sub>x</sub> seed layers using the optimized recipes found during the growth studies (Figure 1). The optimized recipes are shown in Table 3. For each of these

**Table 3. Optimized Recipe for AlO<sub>x</sub> Seed Layer Deposition As Determined by the Growth Studies, Described Further in the Results Section<sup>a</sup>**

| AlO <sub>x</sub> Precursor | ALD Temp (°C) | Precursor Pulse Time (ms) | Precursor Purge time (s) |

|----------------------------|---------------|---------------------------|--------------------------|

| TMA                        | 50            | 30                        | 10                       |

| TEA                        | 100           | 150                       | 1                        |

| TIBA                       | 125           | 150                       | 1                        |

<sup>a</sup>The water pulse and purge times were constant between processes (30 ms and 60 s, respectively).

recipes, the reactor was kept at an operating pressure of 400 mTorr using a 5 sccm flow rate of N<sub>2</sub> carrier gas. Prior to each deposition, the chamber was purged with the sample inside for 10 min.

After the seed layer deposition, we continued with ALD of HfO<sub>2</sub> at 200 °C using tetrakis(dimethylamido) hafnium and H<sub>2</sub>O as the ALD precursors on the seed layer/MoS<sub>2</sub>, to form the TG bilayer insulator. This deposition was carried out in a separate ALD chamber (Fiji F202 from Cambridge Nanotech). Between the AlO<sub>x</sub> and HfO<sub>2</sub> deposition steps, the samples were kept in a N<sub>2</sub> drybox to prevent contamination, and the time between depositions was minimized as much as possible (<24 h). Finally, we deposited a 50 nm Pd layer as the top-gate by electron-beam evaporation. Again, this deposition took place in a separate instrument, so care was taken to prevent contamination between fabrication steps by keeping the samples in a N<sub>2</sub> drybox. In our device structure, we made the top-gate and S/D overlap (approximately 10–20 nm) to minimize the ungated channel resistance. A Janis vacuum probe station (~10<sup>-5</sup> Torr) equipped with a Keithley 4200-SCS parameter analyzer was used for current–voltage (*I*–*V*) characterization and devices were annealed in the probe station vacuum at 150 °C, to remove surface moisture, prior to measurement. All electrical measurements were at room temperature, unless otherwise specified.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsnano.5c10705>.

XPS spectra and stoichiometry analysis of AlO<sub>x</sub> films deposited from TMA, TEA, and TIBA on monolayer MoS<sub>2</sub>; growth per cycle dependence on precursor purge time at 125 °C; SEM images showing nucleation and coverage of AlO<sub>x</sub> on MoS<sub>2</sub> for DMAI, TMA, TEA, and TIBA at the LTF and 125 °C after 10 cycles of ALD; high-resolution SEM of early cycle TIBA nucleation on MoS<sub>2</sub>; transistor transfer characteristics as a function of AlO<sub>x</sub> seed layer thickness for TEA and TIBA. (PDF)

## AUTHOR INFORMATION

### Corresponding Author

**Stacey F. Bent** – Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States; Department of Energy Science & Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0002-1084-5336](https://orcid.org/0000-0002-1084-5336); Email: [sbent@stanford.edu](mailto:sbent@stanford.edu)

## Authors

**Alexander B. Shearer** – Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0002-4128-2636](https://orcid.org/0000-0002-4128-2636)

**Jung-Soo Ko** – Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0009-0006-1890-9038](https://orcid.org/0009-0006-1890-9038)

**Anh Tuan Hoang** – Department of Electrical Engineering and Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-0911-1391](https://orcid.org/0000-0003-0911-1391)

**Andreas Werbrouck** – Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-3796-0024](https://orcid.org/0000-0003-3796-0024)

**Amnon Rothman** – Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0002-7095-8279](https://orcid.org/0000-0002-7095-8279)

**Dea Fackovic Volcanjk** – Department of Chemistry, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-1468-3239](https://orcid.org/0000-0003-1468-3239)

**Yuan-Mau Lee** – Department of Electrical Engineering and Materials Science and Engineering, Stanford University, Stanford, California 94305, United States

**Robert K. A. Bennett** – Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0001-7427-8724](https://orcid.org/0000-0001-7427-8724)

**Andrew J. Mannix** – Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-4788-1506](https://orcid.org/0000-0003-4788-1506)

**Krishna C. Saraswat** – Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States

**Eric Pop** – Department of Electrical Engineering and Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-0436-8534](https://orcid.org/0000-0003-0436-8534)

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsnano.5c10705>

## Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This work was supported by U.S. Department of Energy, award number DE-SC0004782 for AlO<sub>x</sub> ALD development, physisorption-assisted ALD conceptualization, and precursor-dependent nucleation studies (A.B.S., A.W., A.R., D.F.V., S.F.B.). The work was supported in part by Samsung and TSMC through the SystemX Alliance for MoS<sub>2</sub> synthesis and for device fabrication and measurement (J.S.K., A.T.H.). Y.M.L. and E.P. also acknowledge partial support from SUPREME, a JUMP 2.0 center sponsored by the Semiconductor Research Corporation (SRC) and DARPA. We thank Dr. Dongwon Lee at IM&T for his help with transmission electron microscopy images and analysis. This work was performed in part in the Stanford Nanofabrication Facility and the Stanford Nano Shared Facilities, which are supported by the National Science Foundation under award ECCS-1542152 and ECCS-2026822.

## REFERENCES

(1) Jacob, A. P.; Xie, R.; Sung, M. G.; Liebmann, L.; Lee, R. T. P.; Taylor, B. Scaling Challenges for Advanced CMOS Devices. *Int. J. Hi. Spe. Ele. Syst.* **2017**, 26 (01n02), 1740001.

(2) Uchida, K.; Watanabe, H.; Kinoshita, A.; Koga, J.; Numata, T.; Takagi, S. Experimental Study on Carrier Transport Mechanism in Ultrathin-Body SOI Nand p-MOSFETs with SOI Thickness Less than 5 nm. *Digest. International Electron Devices Meeting* **2002**, 47–50.

(3) Kim, Y.-B. Challenges for Nanoscale MOSFETs and Emerging Nanoelectronics. *Transactions on Electrical and Electronic Materials* **2010**, 11 (3), 93–105.

(4) Waldrop, M. M. The Chips Are down for Moore's Law. *Nature News* **2016**, 530 (7589), 144.

(5) Su, S.-K.; Chuu, C.-P.; Li, M.-Y.; Cheng, C.-C.; Wong, H.-S. P.; Li, L.-J. Layered Semiconducting 2D Materials for Future Transistor Applications. *Small Structures* **2021**, 2 (5), 2000103.

(6) Ko, J.-S.; Lee, S.; Bennett, R. K. A.; Schauble, K.; Jaikissoon, M.; Neilson, K.; Hoang, A. T.; Mannix, A. J.; Kim, K.; Saraswat, K. C.; Pop, E. Sub-Nanometer Equivalent Oxide Thickness and Threshold Voltage Control Enabled by Silicon Seed Layer on Monolayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2025**, 25 (7), 2587–2593.

(7) Ko, J.-S.; Shearer, A. B.; Lee, S.; Neilson, K.; Jaikissoon, M.; Kim, K.; Bent, S. F.; Pop, E.; Saraswat, K. C. Achieving 1-Nm-Scale Equivalent Oxide Thickness Top-Gate Dielectric on Monolayer Transition Metal Dichalcogenide Transistors With CMOS-Friendly Approaches. *IEEE Trans. Electron Devices* **2025**, 72 (3), 1514–1519.

(8) George, S. M. Atomic Layer Deposition: An Overview. *Chem. Rev.* **2010**, 110 (1), 111–131.

(9) Leskelä, M.; Ritala, M. Atomic Layer Deposition Chemistry: Recent Developments and Future Challenges. *Angew. Chem., Int. Ed.* **2003**, 42 (45), 5548–5554.

(10) Leskelä, M.; Ritala, M. Atomic Layer Deposition (ALD): From Precursors to Thin Film Structures. *Thin Solid Films* **2002**, 409 (1), 138–146.

(11) Johnson, R. W.; Hultqvist, A.; Bent, S. F. A Brief Review of Atomic Layer Deposition: From Fundamentals to Applications. *Mater. Today* **2014**, 17 (5), 236–246.

(12) Richey, N. E.; de Paula, C.; Bent, S. F. Understanding Chemical and Physical Mechanisms in Atomic Layer Deposition. *J. Chem. Phys.* **2020**, 152 (4), 040902.

(13) Kim, H. G.; Lee, H.-B.-R. Atomic Layer Deposition on 2D Materials. *Chem. Mater.* **2017**, 29 (9), 3809–3826.

(14) Kim, K.; Lee, H.-B.-R.; Johnson, R. W.; Tanskanen, J. T.; Liu, N.; Kim, M.-G.; Pang, C.; Ahn, C.; Bent, S. F.; Bao, Z. Selective Metal Deposition at Graphene Line Defects by Atomic Layer Deposition. *Nat. Commun.* **2014**, 5 (1), 4781.

(15) Zhang, H.; Chiappe, D.; Meerschaut, J.; Conard, T.; Franquet, A.; Nuyttens, T.; Mannarino, M.; Radu, I.; Vandervorst, W.; Delabie, A. Nucleation and Growth Mechanisms of Al<sub>2</sub>O<sub>3</sub> Atomic Layer Deposition on Synthetic Polycrystalline MoS<sub>2</sub>. *J. Chem. Phys.* **2017**, 146 (5), 052810.

(16) Mleczko, M. J.; Zhang, C.; Lee, H. R.; Kuo, H.-H.; Magyari-Köpe, B.; Moore, R. G.; Shen, Z.-X.; Fisher, I. R.; Nishi, Y.; Pop, E. HfSe<sub>2</sub> and ZrSe<sub>2</sub>: Two-Dimensional Semiconductors with Native High- $\kappa$  Oxides. *Science Advances* **2017**, 3 (8), No. e1700481.

(17) Son, S.; Yu, S.; Choi, M.; Kim, D.; Choi, C. Improved High Temperature Integration of Al<sub>2</sub>O<sub>3</sub> on MoS<sub>2</sub> by Using a Metal Oxide Buffer Layer. *Appl. Phys. Lett.* **2015**, 106 (2), 021601.

(18) Li, W.; Zhou, J.; Cai, S.; Yu, Z.; Zhang, J.; Fang, N.; Li, T.; Wu, Y.; Chen, T.; Xie, X.; Ma, H.; Yan, K.; Dai, N.; Wu, X.; Zhao, H.; Wang, Z.; He, D.; Pan, L.; Shi, Y.; Wang, P.; Chen, W.; Nagashio, K.; Duan, X.; Wang, X. Uniform and Ultrathin High- $\kappa$  Gate Dielectrics for Two-Dimensional Electronic Devices. *Nat. Electron* **2019**, 2 (12), 563–571.

(19) Tslev, A.; Sangwan, V. K.; Jariwala, D.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C.; Kalinin, S. V. Near-Field Microwave Microscopy of High- $\kappa$  Oxides Grown on Graphene with an Organic Seeding Layer. *Appl. Phys. Lett.* **2013**, 103 (24), 243105.

(20) Wirtz, C.; Hallam, T.; Cullen, C. P.; Berner, N. C.; O'Brien, M.; Marcia, M.; Hirsch, A.; Duesberg, G. S. Atomic Layer Deposition on 2D Transition Metal Chalcogenides: Layer Dependent Reactivity and Seeding with Organic Ad-Layers. *Chem. Commun.* **2015**, 51 (92), 16553–16556.

(21) Yang, W.; Sun, Q.-Q.; Geng, Y.; Chen, L.; Zhou, P.; Ding, S.-J.; Zhang, D. W. The Integration of Sub-10 nm Gate Oxide on MoS<sub>2</sub> with Ultra Low Leakage and Enhanced Mobility. *Sci. Rep.* **2015**, 5 (1), 11921.

(22) McDonnell, S.; Brennan, B.; Azcatl, A.; Lu, N.; Dong, H.; Buie, C.; Kim, J.; Hinkle, C. L.; Kim, M. J.; Wallace, R. M. HfO<sub>2</sub> on MoS<sub>2</sub> by Atomic Layer Deposition: Adsorption Mechanisms and Thickness Scalability. *ACS Nano* **2013**, 7 (11), 10354–10361.

(23) Price, K. M.; Najmaei, S.; Ekuma, C. E.; Burke, R. A.; Dubey, M.; Franklin, A. D. Plasma-Enhanced Atomic Layer Deposition of HfO<sub>2</sub> on Monolayer, Bilayer, and Trilayer MoS<sub>2</sub> for the Integration of High- $\kappa$  Dielectrics in Two-Dimensional Devices. *ACS Appl. Nano Mater.* **2019**, 2 (7), 4085–4094.

(24) Wang, L.; Travis, J. J.; Cavanagh, A. S.; Liu, X.; Koenig, S. P.; Huang, P. Y.; George, S. M.; Bunch, J. S. Ultrathin Oxide Films by Atomic Layer Deposition on Graphene. *Nano Lett.* **2012**, 12 (7), 3706–3710.

(25) Das, S.; Sebastian, A.; Pop, E.; McClellan, C. J.; Franklin, A. D.; Grasser, T.; Knobloch, T.; Illarionov, Y.; Penumatcha, A. V.; Appenzeller, J.; Chen, Z.; Zhu, W.; Asselberghs, I.; Li, L.-J.; Avci, U. E.; Bhat, N.; Anthopoulos, T. D.; Singh, R. Transistors Based on Two-Dimensional Materials for Future Integrated Circuits. *Nat. Electron* **2021**, 4 (11), 786–799.

(26) Kwak, I.; Kavrik, M.; Park, J. H.; Grissom, L.; Fruhberger, B.; Wong, K. T.; Kang, S.; Kummel, A. C. Low Interface Trap Density in Scaled Bilayer Gate Oxides on 2D Materials via Nanofog Low Temperature Atomic Layer Deposition. *Appl. Surf. Sci.* **2019**, 463, 758–766.

(27) Lee, Y.; Jeon, W.; Cho, Y.; Lee, M.-H.; Jeong, S.-J.; Park, J.; Park, S. Mesostructured Hf<sub>x</sub>Al<sub>y</sub>O<sub>2</sub> Thin Films as Reliable and Robust Gate Dielectrics with Tunable Dielectric Constants for High-Performance Graphene-Based Transistors. *ACS Nano* **2016**, 10 (7), 6659–6666.

(28) Jeong, S.-J.; Kim, H. W.; Heo, J.; Lee, M.-H.; Song, H. J.; Ku, J.; Lee, Y.; Cho, Y.; Jeon, W.; Suh, H.; Hwang, S.; Park, S. Physisorbed-Precursor-Assisted Atomic Layer Deposition of Reliable Ultrathin Dielectric Films on Inert Graphene Surfaces for Low-Power Electronics. *2D Mater.* **2016**, 3 (3), 035027.

(29) Liu, H.; Xu, K.; Zhang, X.; Ye, P. D. The Integration of High- $\kappa$  Dielectrics on Two-Dimensional Crystals by Atomic Layer Deposition. *Appl. Phys. Lett.* **2012**, 100 (15), 152115.

(30) Wu, D.; Zhang, Z.; Lv, D.; Yin, G.; Peng, Z.; Jin, C. High Mobility Top Gated Field-Effect Transistors and Integrated Circuits Based on Chemical Vapor Deposition-Derived Monolayer MoS<sub>2</sub>. *Materials Express* **2016**, 6 (2), 198–204.

(31) Oh, I.-K.; Tanskanen, J.; Jung, H.; Kim, K.; Lee, M. J.; Lee, Z.; Lee, S.-K.; Ahn, J.-H.; Lee, C. W.; Kim, K.; Kim, H.; Lee, H.-B.-R. Nucleation and Growth of the HfO<sub>2</sub> Dielectric Layer for Graphene-Based Devices. *Chem. Mater.* **2015**, 27 (17), 5868–5877.

(32) Smithe, K. K. H.; English, C. D.; Suryavanshi, S. V.; Pop, E. Intrinsic Electrical Transport and Performance Projections of Synthetic Monolayer MoS<sub>2</sub> Devices. *2D Mater.* **2017**, 4 (1), 011009.

(33) Oh, I.-K.; Sandoval, T. E.; Liu, T.-L.; Richey, N. E.; Bent, S. F. Role of Precursor Choice on Area-Selective Atomic Layer Deposition. *Chem. Mater.* **2021**, 33 (11), 3926–3935.

(34) Yarbrough, J.; Bent, S. F. Area-Selective Deposition by Cyclic Adsorption and Removal of 1-Nitropropane. *J. Phys. Chem. A* **2023**, 127 (37), 7858–7868.

(35) Schneider, C. A.; Rasband, W. S.; Eliceiri, K. W. NIH Image to ImageJ: 25 Years of Image Analysis. *Nat. Methods* **2012**, 9 (7), 671–675.

(36) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* **2016**, 16 (6), 3824–3830.

(37) Avrami, M. Kinetics of Phase Change. I General Theory. *J. Chem. Phys.* **1939**, *7* (12), 1103–1112.

(38) Avrami, M. Kinetics of Phase Change. II Transformation-Time Relations for Random Distribution of Nuclei. *J. Chem. Phys.* **1940**, *8* (2), 212–224.

(39) Kolmogorov, A. N. On the statistical theory of crystallization of metals [in Russian]. *Izv. Akad. Nauk SSSR, Ser. Mat.* **1937**, *3*, 355–359.

(40) Johnson, W. A.; Mehl, R. F Reaction kinetics in processes of nucleation and growth. *Trans. Am. Inst. Min. Metall. Eng.* **1939**, *135*, 416–442.

(41) Fanfoni, M.; Tomellini, M. The Johnson-Mehl- Avrami-Kohnogorov Model: A Brief Review. *Nouv Cim D* **1998**, *20* (7), 1171–1182.

(42) Rothman, A.; Werbrouck, A.; Bent, S. F. Enhanced Growth in Atomic Layer Deposition of Ruthenium Metal: The Role of Surface Diffusion and Nucleation Sites. *Chem. Mater.* **2024**, *36* (1), 541–550.

(43) Lee, H.-B.-R.; Mullings, M. N.; Jiang, X.; Clemens, B. M.; Bent, S. F. Nucleation-Controlled Growth of Nanoparticles by Atomic Layer Deposition. *Chem. Mater.* **2012**, *24* (21), 4051–4059.

(44) Parsons, G. N. Functional Model for Analysis of ALD Nucleation and Quantification of Area-Selective Deposition. *Journal of Vacuum Science & Technology A* **2019**, *37* (2), 020911.

(45) Christian, J. W. *The theory of transformations in metals and alloys*; 3rd ed.; Pergamon: Oxford, 2002.

(46) Maue, P.; Chantraine, É.; Pieck, F.; Tonner-Zech, R. Accurately Computed Dimerization Trends of ALD Precursors and Their Impact on Surface Reactivity in Area-Selective Atomic Layer Deposition. *Chem. Mater.* **2025**, *37* (3), 975–988.

(47) Kim, M.; Kim, S.; Shong, B. Adsorption of Dimethylaluminum Isopropoxide (DMAI) on the  $\text{Al}_2\text{O}_3$  Surface: A Machine-Learning Potential Study. *Journal of Science: Advanced Materials and Devices* **2024**, *9* (3), 100754.

(48) Kim, H. G.; Kim, M.; Gu, B.; Khan, M. R.; Ko, B. G.; Yasmeen, S.; Kim, C. S.; Kwon, S.-H.; Kim, J.; Kwon, J.; Jin, K.; Cho, B.; Chun, J.-S.; Shong, B.; Lee, H.-B.-R. Effects of Al Precursors on Deposition Selectivity of Atomic Layer Deposition of  $\text{Al}_2\text{O}_3$  Using Ethanethiol Inhibitor. *Chem. Mater.* **2020**, *32* (20), 8921–8929.

(49) Cho, I.; Yang, J.; Raya, S. S.; Shong, B. Adsorption of Aluminum Precursors on  $\text{MoS}_2$  toward Nucleation of Atomic Layer Deposition. *Colloid and Interface Science Communications* **2025**, *65*, 100823.

(50) Tseng, H.-H.; Kirsch, P.; Park, C. S.; Bersuker, G.; Majhi, P.; Hussain, M.; Jammy, R. The Progress and Challenges of Threshold Voltage Control of High- $\kappa$ /Metal-Gated Devices for Advanced Technologies (Invited Paper). *Microelectron. Eng.* **2009**, *86* (7–9), 1722–1727.

(51) Shin, B.; Weber, J. R.; Long, R. D.; Hurley, P. K.; Van de Walle, C. G.; McIntyre, P. C. Origin and Passivation of Fixed Charge in Atomic Layer Deposited Aluminum Oxide Gate Insulators on Chemically Treated InGaAs Substrates. *Appl. Phys. Lett.* **2010**, *96* (15), 152908.

(52) Kita, K.; Kamata, H.; Fei, J. Interface Dipole Layers between Two Dielectrics: Considerations on Physical Origins and Opportunities to Control Their Formation. In *Extended Abstracts of the 2017 International Conference on Solid State Devices and Materials*; The Japan Society of Applied Physics: Sendai International Center, Sendai Japan, 2017. DOI: [10.7567/SSDM.2017.K-1-01](https://doi.org/10.7567/SSDM.2017.K-1-01).

(53) Abe, Y.; Miyata, N.; Shiraki, Y.; Yasuda, T. Dipole Formation at Direct-Contact  $\text{HfO}_2/\text{Si}$  Interface. *Appl. Phys. Lett.* **2007**, *90* (17), 172906.

(54) Fei, J.; Kita, K. Consideration on the Interfacial Dipole Layer Formation at Non- $\text{SiO}_2$  Oxide Interfaces in the Examples of  $\text{MgO}/\text{Al}_2\text{O}_3$  and  $\text{HfO}_2/\text{Al}_2\text{O}_3$ . In *Extended Abstracts of the 2017 International Conference on Solid State Devices and Materials*; The Japan Society of Applied Physics: Sendai International Center, Sendai Japan, 2017. DOI: [10.7567/SSDM.2017.K-1-03](https://doi.org/10.7567/SSDM.2017.K-1-03).

(55) Cheng, Z.; Pang, C.-S.; Wang, P.; Le, S. T.; Wu, Y.; Shahrijerdi, D.; Radu, I.; Lemme, M. C.; Peng, L.-M.; Duan, X.; Chen, Z.; Appenzeller, J.; Koester, S. J.; Pop, E.; Franklin, A. D.; Richter, C. A. How to Report and Benchmark Emerging Field-Effect Transistors. *Nat. Electron.* **2022**, *5* (7), 416–423.

(56) Liang, J.; Xu, K.; Toncini, B.; Bersch, B.; Jariwala, B.; Lin, Y.-C.; Robinson, J.; Fullerton-Shirey, S. K. Impact of Post-Lithography Polymer Residue on the Electrical Characteristics of  $\text{MoS}_2$  and  $\text{WSe}_2$  Field Effect Transistors. *Advanced Materials Interfaces* **2019**, *6* (3), 1801321.

(57) Bolshakov, P.; Smyth, C. M.; Khosravi, A.; Zhao, P.; Hurley, P. K.; Hinkle, C. L.; Wallace, R. M.; Young, C. D. Contact Engineering for Dual-Gate  $\text{MoS}_2$  Transistors Using  $\text{O}_2$  Plasma Exposure. *ACS Appl. Electron. Mater.* **2019**, *1* (2), 210–219.

(58) Mahlouji, R.; Zhang, Y.; Verheijen, M. A.; Karwal, S.; Hofmann, J. P.; Kessels, W. M. M.; Bol, A. A. Influence of High- $\kappa$  Dielectrics Integration on ALD-Based  $\text{MoS}_2$  Field-Effect Transistor Performance. *ACS Appl. Nano Mater.* **2024**, *7* (16), 18786–18800.

(59) Wilk, G. D.; Wallace, R. M.; Anthony, J. M. High- $\kappa$  Gate Dielectrics: Current Status and Materials Properties Considerations. *J. Appl. Phys.* **2001**, *89* (10), 5243–5275.

(60) Weber, J. R.; Janotti, A.; Van de Walle, C. G. Native Defects in  $\text{Al}_2\text{O}_3$  and Their Impact on III-V/ $\text{Al}_2\text{O}_3$  Metal-Oxide-Semiconductor-Based Devices. *J. Appl. Phys.* **2011**, *109* (3), 033715.

(61) Vandana; Batra, N.; Gope, J.; Singh, R.; Panigrahi, J.; Tyagi, S.; Pathi, P.; Srivastava, S. K.; Rauthan, C. M. S.; Singh, P. K. Effect of Low Thermal Budget Annealing on Surface Passivation of Silicon by ALD Based Aluminum Oxide Films. *Phys. Chem. Chem. Phys.* **2014**, *16* (39), 21804–21811.

(62) Buckley, J.; De Salvo, B.; Deleruyelle, D.; Gely, M.; Nicotra, G.; Lombardo, S.; Damlecourt, J. F.; Hollinger, Ph.; Martin, F.; Deleonibus, S. Reduction of Fixed Charges in Atomic Layer Deposited  $\text{Al}_2\text{O}_3$  Dielectrics. *Microelectron. Eng.* **2005**, *80*, 210–213.

(63) Kang, J.; Lee, E.-C.; Chang, K. J.; Jin, Y.-G. H-Related Defect Complexes in  $\text{HfO}_2$ : A Model for Positive Fixed Charge Defects. *Appl. Phys. Lett.* **2004**, *84* (19), 3894–3896.

(64) Sreenivasan, R.; McIntyre, P. C.; Kim, H.; Saraswat, K. C. Effect of Impurities on the Fixed Charge of Nanoscale  $\text{HfO}_2$  Films Grown by Atomic Layer Deposition. *Appl. Phys. Lett.* **2006**, *89* (11), 112903.

(65) Gavartin, J. L.; Ramo, D. M.; Shluger, A. L.; Bersuker, G.; Lee, B. H. Negative Oxygen Vacancies in  $\text{HfO}_2$  as Charge Traps in High- $\kappa$  Stacks. *Appl. Phys. Lett.* **2006**, *89* (8), 082908.

(66) Gu, D.; Dey, S. K.; Majhi, P. Effective Work Function of Pt, Pd, and Re on Atomic Layer Deposited  $\text{HfO}_2$ . *Appl. Phys. Lett.* **2006**, *89* (8), 082907.

(67) Aghamohammadi, M.; Rödel, R.; Zschieschang, U.; Ocal, C.; Boschker, H.; Weitz, R. T.; Barrena, E.; Klauk, H. Threshold-Voltage Shifts in Organic Transistors Due to Self-Assembled Monolayers at the Dielectric: Evidence for Electronic Coupling and Dipolar Effects. *ACS Appl. Mater. Interfaces* **2015**, *7* (41), 22775–22785.

(68) Vasudevan, S.; Kapur, N.; He, T.; Neurock, M.; Tour, J. M.; Ghosh, A. W. Controlling Transistor Threshold Voltages Using Molecular Dipoles. *J. Appl. Phys.* **2009**, *105* (9), 093703.

(69) Illarionov, Y. Y.; Knobloch, T.; Jech, M.; Lanza, M.; Akinwande, D.; Vexler, M. I.; Mueller, T.; Lemme, M. C.; Fiori, G.; Schwierz, F.; Grasser, T. Insulators for 2D Nanoelectronics: The Gap to Bridge. *Nat. Commun.* **2020**, *11* (1), 3385.

(70) Xu, Y.; Liu, T.; Liu, K.; Zhao, Y.; Liu, L.; Li, P.; Nie, A.; Liu, L.; Yu, J.; Feng, X.; Zhuge, F.; Li, H.; Wang, X.; Zhai, T. Scalable Integration of Hybrid High- $\kappa$  Dielectric Materials on Two-Dimensional Semiconductors. *Nat. Mater.* **2023**, *22* (9), 1078–1084.

(71) Uchiyama, H.; Maruyama, K.; Chen, E.; Nishimura, T.; Nagashio, K. A Monolayer  $\text{MoS}_2$  FET with an EOT of 1.1 nm Achieved by the Direct Formation of a High- $\kappa$   $\text{Er}_2\text{O}_3$  Insulator Through Thermal Evaporation. *Small* **2023**, *19* (15), 2207394.

(72) Ko, J.-S.; Zhang, Z.; Lee, S.; Jaikisssoon, M.; Bennett, R. K. A.; Kim, K.; Kummel, A. C.; Bandaru, P.; Pop, E.; Saraswat, K. C. Ultrathin Gate Dielectric Enabled by Nanofog Aluminum Oxide on Monolayer  $\text{MoS}_2$ . *ESSDERC 2023 - IEEE 53rd European Solid-State Device Research Conference (ESSDERC)* **2023**, 1–4.

(73) Lee, T.-E.; Su, Y.-C.; Lin, B.-J.; Chen, Y.-X.; Yun, W.-S.; Ho, P.-H.; Wang, J.-F.; Su, S.-K.; Hsu, C.-F.; Mao, P.-S.; Chang, Y.-C.; Chien, C.-H.; Liu, B.-H.; Su, C.-Y.; Kei, C.-C.; Wang, H.; Philip Wong, H.-S.; Lee, T. Y.; Chang, W.-H.; Cheng, C.-C.; Radu, I. P. Nearly Ideal Subthreshold Swing in Monolayer MoS<sub>2</sub> Top-Gate nFETs with Scaled EOT of 1 nm. *2022 International Electron Devices Meeting (IEDM) 2022*, 7.4.1–7.4.4.

(74) Ko, J.-S.; Shearer, A.; Lee, S.; Neilson, K.; Jaikissoon, M.; Kim, K.; Bent, S.; Saraswat, K.; Pop, E. Achieving 1-nm-Scale Equivalent Oxide Thickness Top Gate Dielectric on Monolayer Transition Metal Dichalcogenide Transistors with CMOS-Friendly Approaches. In *2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits)*; IEEE: Honolulu, HI, USA, 2024; pp 1–2. DOI: 10.1109/VLSITechnologyandCir46783.2024.10631360.

(75) Patoary, N. H.; Mamun, F. A.; Xie, J.; Grasser, T.; Sanchez Esqueda, I. Analysis and EOT Scaling on Top- and Double-Gate 2D CVD-Grown Monolayer MoS<sub>2</sub> FETs. *Advanced Electronic Materials n/a* (n/a), 2400152. DOI: 10.1002/aelm.202400152.

(76) Arutchelvan, G.; Smets, Q.; Verreck, D.; Ahmed, Z.; Gaur, A.; Sutar, S.; Jussot, J.; Groven, B.; Heyns, M.; Lin, D.; Asselberghs, I.; Radu, I. Impact of Device Scaling on the Electrical Properties of MoS<sub>2</sub> Field-Effect Transistors. *Sci. Rep.* **2021**, 11 (1), 6610.

(77) Lin, Z.; Wu, X.; Cott, D.; Shi, Y.; Medina Silva, H.; Sergeant, S.; Conard, T.; Meersschaert, J.; Nalin Mehta, A.; Groven, B.; Morin, P.; Asselberghs, I.; Lockhart de la Rosa, C. J.; Kar, G. S.; Lin, D.; Delabie, A. Top-Gate Stack Engineering Featuring a High- $\kappa$  Gadolinium Aluminate Interfacial Layer for Field-Effect Transistors Based on Two-Dimensional Transition-Metal Dichalcogenides. *ACS Appl. Electron. Mater.* **2024**, 6 (6), 4213–4222.

(78) Chang, W. H.; Okada, N.; Horikawa, M.; Endo, T.; Miyata, Y.; Irisawa, T. ALD-ZrO<sub>2</sub> Gate Dielectric with Suppressed Interfacial Oxidation for High Performance MoS<sub>2</sub> Top Gate MOSFETs. *Jpn. J. Appl. Phys.* **2021**, 60 (SB), SBBH03.

(79) Ninomiya, N.; Mori, T.; Uchida, N.; Watanabe, E.; Tsuya, D.; Moriyama, S.; Tanaka, M.; Ando, A. Fabrication of High- $\kappa$ /Metal-Gate MoS<sub>2</sub> Field-Effect Transistor by Device Isolation Process Utilizing Ar-Plasma Etching. *Jpn. J. Appl. Phys.* **2015**, 54 (4), 046502.

(80) Bhattacharjee, S.; Ganapathi, K. L.; Mohan, S.; Bhat, N. (Invited) Interface Engineering of High- $\kappa$  Dielectrics and Metal Contacts for High Performance Top-Gated MoS<sub>2</sub> FETs. *ECS Trans.* **2017**, 80 (1), 101.

(81) Huang, J.-K.; Wan, Y.; Shi, J.; Zhang, J.; Wang, Z.; Wang, W.; Yang, N.; Liu, Y.; Lin, C.-H.; Guan, X.; Hu, L.; Yang, Z.-L.; Huang, B.-C.; Chiu, Y.-P.; Yang, J.; Tung, V.; Wang, D.; Kalantar-Zadeh, K.; Wu, T.; Zu, X.; Qiao, L.; Li, L.-J.; Li, S. High- $\kappa$  Perovskite Membranes as Insulators for Two-Dimensional Transistors. *Nature* **2022**, 605 (7909), 262–267.

(82) Li, L.; Zheng, H.; Xiang, H.; Chien, Y.-C.; Ang, K.-W. Novel MoS<sub>2</sub> Dual-Gate FET with a Highly Scaled EOT of 2.4 nm High- $\kappa$  Gate Dielectric Layer for Reconfigurable Logic Gate and High-Precision Analog Synapse. *2023 Silicon Nanoelectronics Workshop (SNW) 2023*, 105–106.

(83) Zeng, D.; Zhang, Z.; Xue, Z.; Zhang, M.; Chu, P. K.; Mei, Y.; Tian, Z.; Di, Z. Single-Crystalline Metal-Oxide Dielectrics for Top-Gate 2D Transistors. *Nature* **2024**, 632 (8026), 788–794.

(84) English, C. D.; Smithe, K. K. H.; Xu, R. L.; Pop, E. Approaching Ballistic Transport in Monolayer MoS<sub>2</sub> Transistors with Self-Aligned 10 nm Top Gates. *2016 IEEE International Electron Devices Meeting (IEDM) 2016*, 5.6.1–5.6.4.

#### CAS INSIGHTS™

## EXPLORE THE INNOVATIONS SHAPING TOMORROW

Discover the latest scientific research and trends with CAS Insights. Subscribe for email updates on new articles, reports, and webinars at the intersection of science and innovation.

[Subscribe today](#)

# Precursor Engineering of Atomic Layer Deposition for Top-Gate Insulators on Monolayer MoS<sub>2</sub> Transistors

Alexander B. Shearer<sup>1</sup>, Jung-Soo Ko<sup>2</sup>, Anh Tuan Hoang<sup>2,3</sup>, Andreas Werbrouck<sup>1</sup>, Amnon Rothman<sup>1</sup>, Dea Fackovic Volcanjk<sup>4</sup>, Yuan-Mau Lee<sup>2,3</sup>, Robert K. A. Bennett<sup>2</sup>, Andrew J. Mannix<sup>3</sup>, Krishna C. Saraswat<sup>2</sup>, Eric Pop<sup>2,3</sup>, Stacey F. Bent<sup>1,5</sup>

<sup>1</sup>*Department of Chemical Engineering, Stanford University, Stanford, CA, 94305, USA*

<sup>2</sup>*Department of Electrical Engineering, Stanford University, Stanford, CA, 94305, USA*

<sup>3</sup>*Materials Science and Engineering, Stanford University, Stanford, CA, 94305, USA*

<sup>4</sup>*Department of Chemistry, Stanford University, Stanford, CA, 94305, USA*

<sup>5</sup>*Department of Energy Science and Engineering, Stanford University, Stanford, CA, 94305, USA*

**Keywords:** Atomic layer deposition, precursor engineering, physisorption, 2D materials, transmission metal dichalcogenides, transistor

## Supplementary Information

**Figure S1.** XPS spectra of TMA-, TEA-, and TIBA-based AlO<sub>x</sub> grown on 1L MoS<sub>2</sub> at the lowest temperature feasible (LTF) for each precursor (50 °C, 100 °C, and 125 °C, respectively). For each precursor, 35 cycles of ALD were performed, corresponding to ~3.5 nm for TIBA, ~4.5 nm for TEA, and ~5 nm for TMA. The stoichiometries of the AlO<sub>x</sub> films grown by different precursors, as extracted from the XPS spectra, are shown in the legend.

### **SI Discussion 1: Stoichiometry of ALD AlO<sub>x</sub> on MoS<sub>2</sub> by different precursors.**