# High-Field Breakdown and Thermal Characterization of Indium Tin Oxide Transistors

Haotian Su, Yuan-Mau Lee, Tara Peña, Sydney Fultz-Waters, Jimin Kang, Çağıl Köroğlu, Sumaiya Wahid, Christina J. Newcomb, Young Suh Song, H.-S. Philip Wong, Shan X. Wang, and Eric Pop\*

Cite This: *ACS Nano* 2025, 19, 16794–16802

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

**ABSTRACT:** Amorphous oxide semiconductors are gaining interest for logic and memory transistors compatible with low-temperature fabrication. However, their low thermal conductivity and heterogeneous interfaces suggest that their performance may be severely limited by self-heating, especially at higher power and device densities. Here, we investigate the high-field breakdown of ultrathin (~4 nm) amorphous indium tin oxide (ITO) transistors with scanning thermal microscopy (SThM) and multiphysics simulations. The ITO devices break irreversibly at channel temperatures of ~180 and ~340 °C on  $\text{SiO}_2$  and  $\text{HfO}_2$  substrates, respectively, with failure primarily caused by thermally-induced compressive strain near the device contacts. Combining SThM measurements with simulations allows us to estimate a thermal boundary conductance of  $35 \pm 12 \text{ MWm}^{-2}\text{K}^{-1}$  for ITO on  $\text{SiO}_2$  and  $51 \pm 14 \text{ MWm}^{-2}\text{K}^{-1}$  for ITO on  $\text{HfO}_2$ . The latter also enables significantly higher breakdown power due to better heat dissipation and closer thermal expansion matching. These findings provide insights into the thermo-mechanical limitations of indium-based amorphous oxide transistors, which are important for more reliable and high-performance logic and memory applications.

**KEYWORDS:** high-field breakdown, ITO transistor, nanoscale thermometry, SThM, strain

## INTRODUCTION

Amorphous oxide semiconductors (AOS) are well-established in the display industry<sup>1–3</sup> and are increasingly recognized as promising back-end-of-line (BEOL)-compatible channel materials for thin-film transistors.<sup>4–6</sup> Among them, indium tin oxide (ITO) transistors stand out due to their low-temperature large-scale deposition methods, high drive current, and low leakage, making them promising for *n*-type BEOL logic and memory applications.<sup>5–10</sup> However, their performance and stability could be limited by self-heating during operation,<sup>10–15</sup> with heat dissipation challenges potentially worsened by high power densities and high device densities.<sup>16–19</sup>

Broadly speaking, thermal management is a critical challenge across all modern electronics, impacting not only transistor performance<sup>20–22</sup> but also memory,<sup>23,24</sup> displays,<sup>25–27</sup> and integrated circuit reliability,<sup>28–30</sup> as well as flexible electronics<sup>31,32</sup> where self-heating is amplified by the low thermal conductivity of the substrates. To address these thermal challenges in oxide transistors, various strategies have been explored. Liao et al.<sup>13</sup> incorporated an interlayer between the

transistor channel and substrate to facilitate device heat dissipation, Besleaga et al.<sup>33</sup> employed a gate dielectric with high thermal conductivity to reduce self-heating, while Kise et al.<sup>34</sup> implemented a U-shaped transistor design to reduce self-heating. Furthermore, high thermal conductivity substrates, such as high-resistivity Si, SiC, and diamond, have also been explored to aid heat dissipation and alleviate self-heating effects.<sup>10,12,14,35</sup>

Despite these advancements, the heat dissipation and breakdown mechanisms in ITO transistors remain poorly understood. Moreover, the thermal boundary conductance (TBC) at the interface between the ITO channel and its dielectric, essential for transistor heat dissipation,<sup>32,36–38</sup> is

Received: January 24, 2025

Revised: March 25, 2025

Accepted: March 26, 2025

Published: April 22, 2025

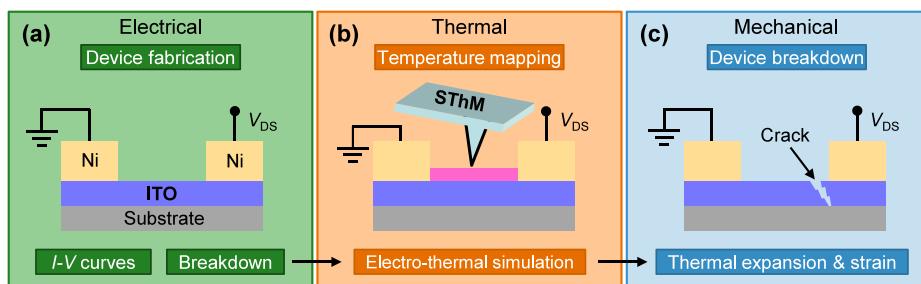

**Figure 1.** Overview of our electro-thermo-mechanical multiphysics approach. Electrical analysis begins with (a) ITO transistor fabrication, measuring current–voltage up to device breakdown. Thermal analysis in (b) is done with scanning thermal microscopy (SThM), combined with finite-element electro-thermal modeling, to extract thermal properties such as the thermal boundary conductance (TBC) of the ITO- $\text{SiO}_2$  interface. Solid mechanics simulations, (c), reveal thermal expansion and peak strain distributions which appear consistent with images of cracks forming in the ITO channel, leading to device failure.

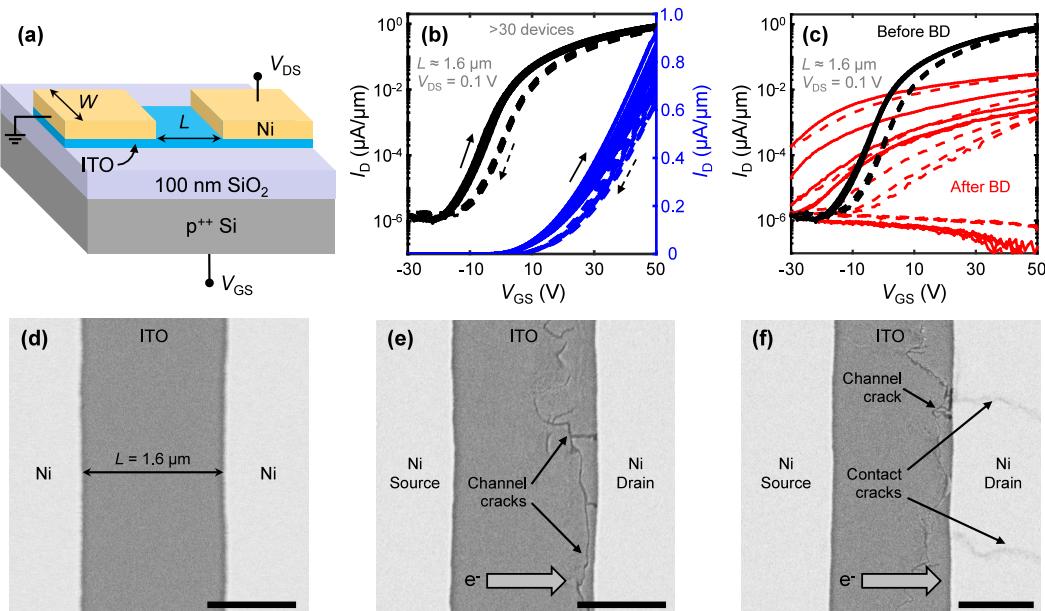

**Figure 2.** (a) Schematic of back-gated ITO transistors, with 4 nm thin ITO channel on  $\text{SiO}_2$  (100 nm)/ $\text{Si}$  ( $\text{p}^{++}$ ) substrate, and 80 nm Ni source and drain contacts. (b) Measured transfer curves from >30 devices with channel length  $L \approx 1.6 \mu\text{m}$ , on log (black) and linear scale (blue). (c) Transfer curves for a subset of 10 devices before (black) and after (red) breakdown (BD), showing significant reduction of on-state  $I_D$  and loss of gate control. Solid/dashed lines mark forward/backward  $V_{GS}$  sweeps. (d) Scanning electron microscopy (SEM) image of initial ITO transistor channel compared with (e) SEM image of a device after breakdown showing channel cracks, and (f) another device showing additional cracks under the Ni drain. Scale bars in (d–f) are all 1  $\mu\text{m}$ . Block arrows in (e,f) show direction of electron flow.

underexplored. Techniques like thermoreflectance imaging and time-domain thermoreflectance have been widely used to study the thermal properties of devices and thin films.<sup>12,35,39–41</sup> However, their limitations, such as low spatial resolution (i.e., spot size greater than transistor dimensions) and considerable uncertainties in TBC measurements for interfaces between ultrathin amorphous films, highlight the need for alternative approaches to understand the thermal properties and breakdown mechanisms of ITO transistors.

In this study, we fabricate ITO transistors with 4 nm thin sputtered channels and investigate their breakdown during high-field operation. Using scanning thermal microscopy (SThM),<sup>42,43</sup> we measure the ITO channel temperature during operation and, through simulations, quantify the TBC at ITO- $\text{SiO}_2$  and ITO- $\text{HfO}_2$  interfaces. These interfaces limit heat dissipation and, along with their thermal expansion mismatch, contribute to localized compressive strain. Our analysis reveals that ITO transistor breakdown is driven by thermally

accelerated cracks that appear near the ITO channel/contact edges. These findings provide insights into the thermo-mechanical limitations of ITO transistors and inform the design of more reliable future devices, with implications for the broader nanotechnology community working on thermal management and reliability in nanoscale devices.

## RESULTS AND DISCUSSION

We employ an electro-thermo-mechanical multiphysics approach to investigate the failure mechanisms and heat dissipation in ITO transistors, as depicted in Figure 1. Electrical analysis begins with the fabrication of back-gated ITO transistors, using a 4 nm thick sputtered ITO channel on a  $\text{SiO}_2$  (100 nm) on  $\text{p}^{++}$  Si substrate with Ni top contacts. The highly doped Si substrate is also used as the back-gate and more fabrication details can be found in S. Wahid et al.,<sup>9</sup> as well as in our **Methods** section and Supporting Information **Section S1**. Nearly one hundred devices were characterized

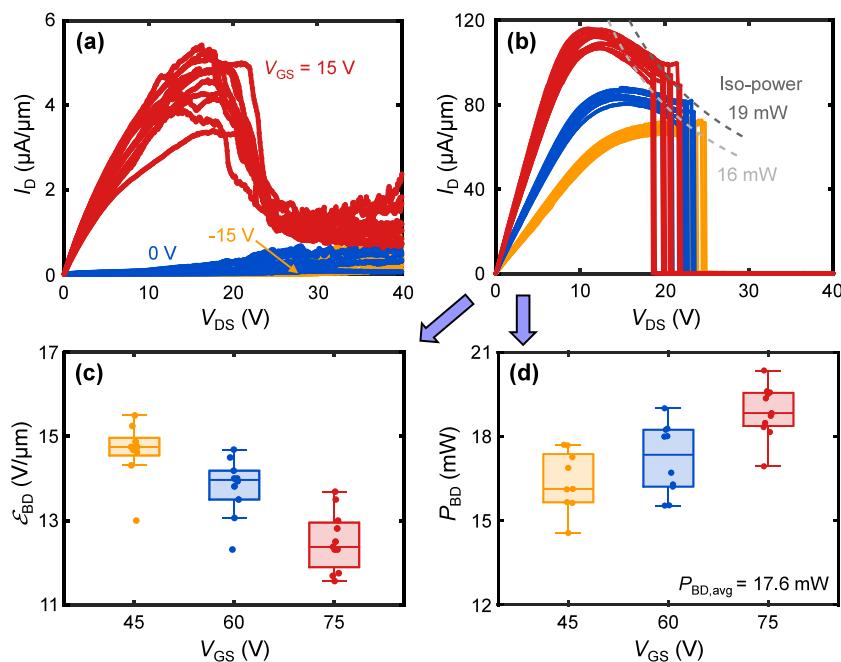

**Figure 3.** (a) Measured current vs drain voltage ( $I_D$  vs  $V_{DS}$ ) curves of ITO transistors in subthreshold or low overdrive ( $V_{GS} = -15, 0, 15$  V). (b)  $I_D$  vs  $V_{DS}$  breakdown of ITO transistors at high  $V_{GS} = 45, 60, 75$  V, showing an abrupt  $I_D$  drop around  $V_{DS} \approx 20$  V;  $\sim 10$  devices were measured for each  $V_{GS}$ . Dashed lines mark the range of power dissipation at device breakdown. (c) Average lateral electric field at device breakdown ( $\varepsilon_{BD}$ ) along the ITO channel, from the three  $V_{GS}$  conditions in (b). (d) Breakdown power ( $P_{BD}$ ) under the same breakdown  $V_{GS}$  in (b), with average breakdown power  $P_{BD,avg} \approx 17.6$  mW. We note that all electrical measurements in this work are performed in direct current (DC) mode, to simplify the thermal analysis and keep them consistent with the SThM measurements. Pulsed measurements<sup>49–51</sup> could, in principle, be used to study operation with reduced self-heating, but they are impractical here because the electrical time constant of our devices, which is dominated by the large pad capacitance, is much greater than their thermal time constant, which is expected to be around  $\sim 30$  ns, dominated by the  $\text{SiO}_2$  substrate.<sup>52</sup>

electrically, up to their breakdown, with channel lengths ( $L$ ) between 1.5 and 1.7  $\mu\text{m}$  and widths of 10  $\mu\text{m}$ .

To map the device temperature during operation we used SThM,<sup>37,44–46</sup> which has sub-100 nm spatial resolution, depending on the probing tip and environmental conditions. (Raman thermometry<sup>37,45,46</sup> appears impractical with the ultrathin amorphous ITO, which does not have a usable Raman signal.) These thermal measurements were complemented with finite-element modeling,<sup>23,32,37</sup> which enabled simulation of device temperatures and estimation of some unknown parameters, such as TBC. Simulations of mechanical strain distributions across the transistor<sup>47,48</sup> were also conducted to assess the impact of thermal expansion during operation. Comparing these simulations with experimental observations of device failure correlates electrical performance, heat dissipation, and mechanical reliability in our ITO devices.

**Electrical Characterization.** ITO transistors with the geometry illustrated in Figure 2a were fabricated and characterized to evaluate their electrical performance and breakdown. Transfer curves ( $I_D$  vs  $V_{GS}$ ) shown in Figure 2b were measured for  $>30$  devices with channel length of  $\sim 1.6$   $\mu\text{m}$ , revealing relatively low variability. Breakdown measurements were conducted on a subset of 10 devices by applying  $V_{GS} = 45$  V and sweeping  $V_{DS}$  from 0 to 40 V. Transfer curves measured after breakdown, in Figure 2c, show much lower on-state current and loss of gate control. Electrical characterization details are provided in the Methods section. Scanning electron microscopy (SEM) images further reveal the physical damage in these transistors: Figure 2d compares an original device channel with failed devices in Figure 2e (prominent cracks in

the ITO channel near the drain) and Figure 2f (additional cracks in the Ni drain contact).

Current vs drain voltage ( $V_{DS}$ ) measurements up to device breakdown are shown in Figure 3a,b, with different gate voltages ( $V_{GS}$ ); in Figure 3a, devices are operated below threshold ( $V_{GS} = -15, 0$  V) and at smaller overdrive ( $V_{GS} = 15$  V). Below threshold,  $I_D$  increases weakly with  $V_{DS}$  due to carrier extraction from trap states under increasing lateral electric field, consistent with previous reports for AOS-based power devices.<sup>53–55</sup> However, for device breakdowns in the on-state (Figure 3b with  $V_{GS} = 45, 60, 75$  V), an abrupt current drop is observed at  $V_{DS} \approx 20$  V, similar to breakdown behavior recently reported in  $\sim 10$  times larger and thicker IGZO devices.<sup>56</sup> Additional details on transfer curves and gate leakage before and after breakdown are provided in Supporting Information Section S2. The average electric field at breakdown ( $\varepsilon_{BD}$ ) along the ITO channel decreases with increasing  $V_{GS}$  (Figure 3c), suggesting that the breakdown is initiated by higher current and higher temperature (i.e., higher carrier density at higher  $V_{GS}$ ) rather than the lateral electric field acting alone. The corresponding breakdown power ( $P_{BD}$ ) in Figure 3d displays a weak increase with  $V_{GS}$ , which is consistent with improved field uniformity as the transistor breaks down deeper in the linear regime at higher  $V_{GS}$ . Nevertheless, as we will later see, the ITO channel breakdown mechanism is more complex.

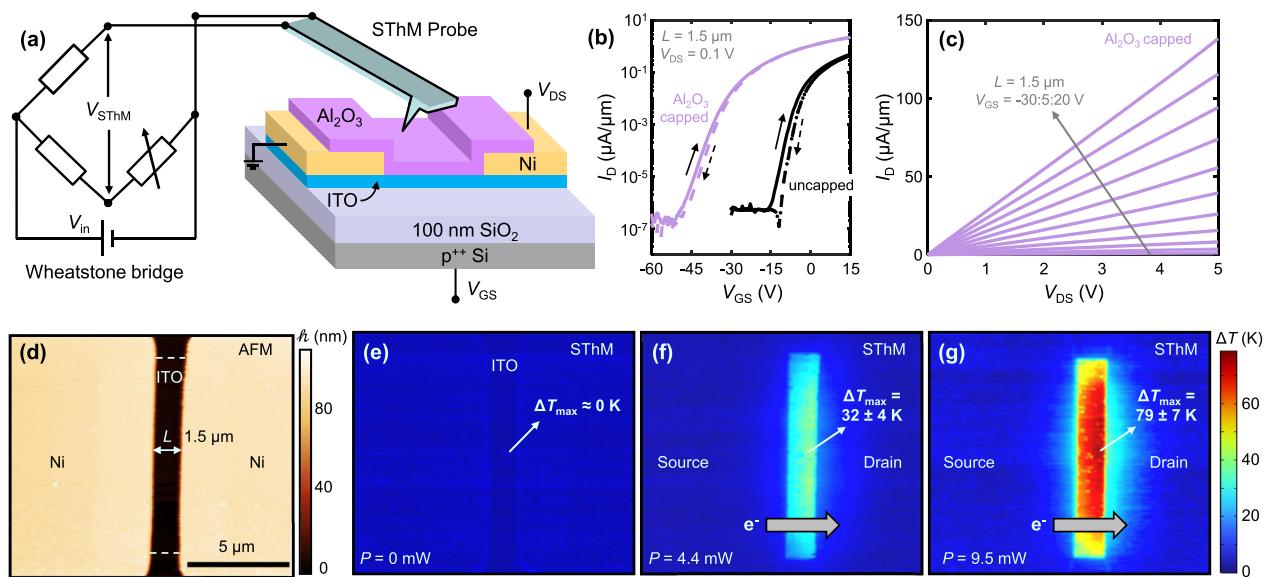

**Thermal Characterization.** To evaluate the device temperature during operation, we employ scanning thermal microscopy (SThM). The experimental setup, shown schematically in Figure 4a, utilizes a Wheatstone bridge to

**Figure 4.** (a) Schematic of SThM measurement on ITO transistors, showing a Wheatstone bridge connected to the SThM cantilever. The tip scans in contact mode with the top device surface. (b) Measured transfer curves of uncapped (black) and  $\text{Al}_2\text{O}_3$ -capped (purple) devices, showing negative shift in threshold voltage consistent with our previous work.<sup>9</sup> Solid/dashed lines mark forward/backward  $V_{\text{GS}}$  sweeps. (c) Measured  $I_{\text{D}}$  vs  $V_{\text{DS}}$  curve of  $\text{Al}_2\text{O}_3$ -capped devices, showing linear behavior. (d) AFM topography scan of an ITO transistor, and corresponding SThM temperature map at input powers of: (e) 0 mW, (f) 4.4 mW, and (g) 9.5 mW. The block arrow shows the direction of electron flow, from source to drain. At an input power of 9.5 mW, the maximum ITO temperature rise ( $\Delta T_{\text{max}}$ , above room temperature) is  $79 \pm 7$  K, as shown in (g).

connect the SThM cantilever, which operates in contact mode. Devices were capped with a 6 nm  $\text{Al}_2\text{O}_3$  layer to prevent direct electrical contact<sup>37,44,45</sup> between the SThM probe and ITO channel. More details on the SThM setup and calibration are provided in the **Methods** section and Supporting Information **Section S3**. The transfer curves of uncapped and  $\text{Al}_2\text{O}_3$ -capped devices (Figure 4b) reveal a negative shift in threshold voltage for the capped devices, consistent with our prior findings.<sup>9</sup> This capping layer has negligible impact on the ITO channel temperature measured by SThM.<sup>37</sup> For SThM measurements, to prevent device damage or breakdown, the devices were measured in the linear  $I_{\text{D}}$  vs  $V_{\text{DS}}$  region, a subset of which is shown in Figure 4c.

The atomic force microscopy (AFM) topography scan of an ITO transistor with 1.5  $\mu\text{m}$  long channel is shown in Figure 4d. The corresponding SThM maps (Figures 4e–g) display temperature distributions at different input powers,  $P = I_{\text{D}}V_{\text{DS}}$ . Figure 4e, at 0 mW, displays the background temperature rise  $\sim 0$  K, as expected. At 4.4 and 9.5 mW input powers,  $\Delta T_{\text{max}}$  reaches  $32 \pm 4$  and  $79 \pm 7$  K, respectively. The uncertainties arise from SThM calibration, with more details in Supporting Information **Section S3**. The measured temperature is slightly higher near the drain contact (Figure 4g), which is expected due to the direction of electron flow.<sup>37</sup> (The electron density is lower and the lateral field is higher near the drain.) The temperature drops rapidly at the Ni contacts, which function as heat sinks.

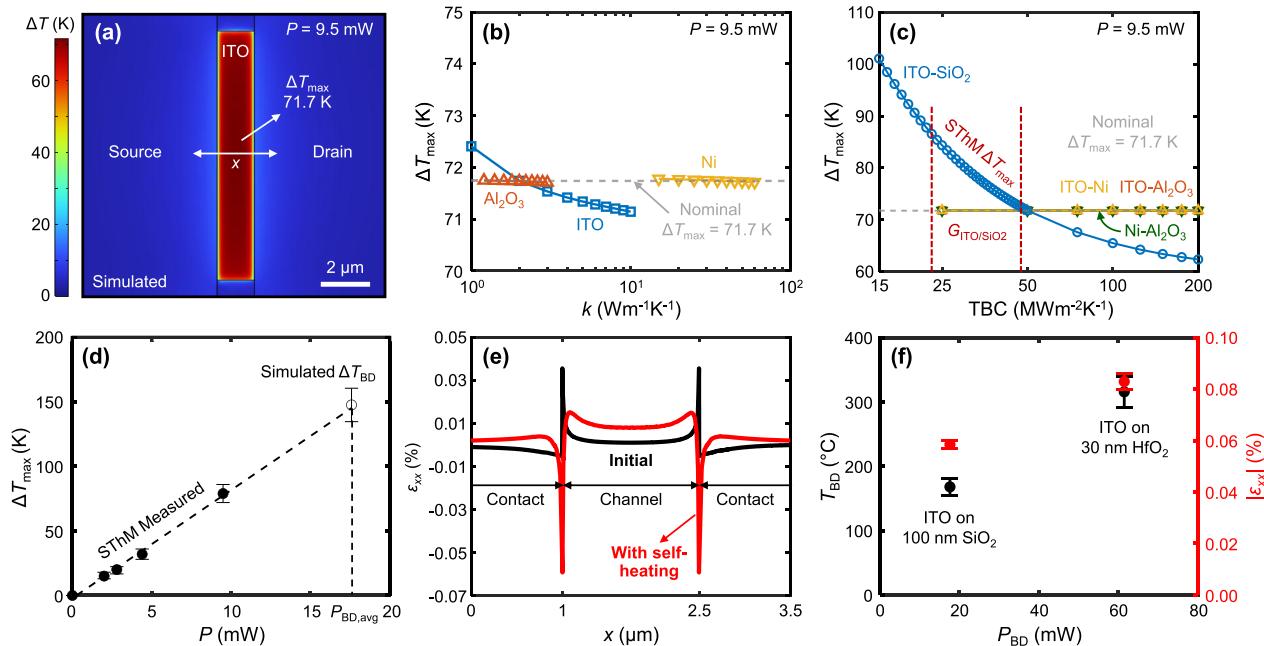

**Electro-Thermo-Mechanical Modeling.** We also carried out finite-element simulations<sup>23,32,37</sup> to complement the SThM measurements and understand the heat dissipation characteristics of ITO transistors, with modeling details in the **Methods** section. The simulated temperature map with 9.5 mW input power is shown in Figure 5a, revealing a peak temperature rise  $\Delta T_{\text{max}} = 71.7$  K. This simulation uses thermal conductivity ( $k$ ) and thermal boundary conductance (TBC) values detailed in

Supporting Information **Section S4**, and it assumes uniform power dissipation across the device channel, which is a good approximation for a device operating in the linear region.<sup>57</sup> This approximation does not capture the subtle temperature rise near the drain seen experimentally (Figure 4g), but is sufficiently good to yield an *average* estimate of the TBC (between ITO and its substrate), which dominates heat flow. We also performed a sensitivity analysis with respect to some of the key thermal simulation parameters—as shown in Figure 5b,  $\Delta T_{\text{max}}$  has negligible dependence on practical  $k$  ranges for  $\text{Al}_2\text{O}_3$ , Ni, and ITO. Similarly, Figure 5c indicates that wide TBC variations (25–250  $\text{MWm}^{-2}\text{K}^{-1}$ ) for ITO-Ni, ITO- $\text{Al}_2\text{O}_3$ , and Ni- $\text{Al}_2\text{O}_3$  interfaces have minimal impact on  $\Delta T_{\text{max}}$ , suggesting those interfaces play a minimal role in heat sinking. However,  $\Delta T_{\text{max}}$  is strongly dependent on the TBC of the ITO- $\text{SiO}_2$  interface, which is estimated to be  $35 \pm 12$   $\text{MWm}^{-2}\text{K}^{-1}$ , by comparing our simulations with SThM measurements of the peak temperature ( $79 \pm 7$  K in Figure 4g) for this power input. The  $\text{TBC}_{\text{ITO-SiO}_2}$  estimated here is consistent with other TBCs reported for similar interfaces.<sup>13,58</sup>

Figure 5d shows the relationship between  $\Delta T_{\text{max}}$  and input power ( $P$ ), demonstrating good agreement between temperatures measured by SThM and simulated temperature at the average breakdown power ( $P_{\text{BD,avg}}$ ) determined in Figure 3d). The average breakdown temperature ( $T_{\text{BD}}$ ) of our ITO transistors on 100 nm  $\text{SiO}_2$ /Si substrate is found to be  $\sim 155$ – $181$  °C. This temperature is lower than the annealing temperature of ITO transistors,<sup>8,9</sup> which can reach up to 300 °C. Therefore, we cannot attribute the breakdown of our ITO transistors solely to the temperature rise during operation, and other mechanisms must be at play. To understand other effects, we also carried out thermo-mechanical simulations, displaying the estimated strain distribution along the ITO channel,  $\varepsilon_{\text{xx}}$  before current flow (black line) and after  $P_{\text{BD,avg}}$  is applied (red line), as shown in Figure 5e. Initially, tensile strain

**Figure 5.** (a) Simulated temperature map of ITO transistor with 9.5 mW input power, showing peak temperature rise  $\Delta T_{\max} = 71.7$  K, with nominal thermal parameters provided in Supporting Information Section S4. (b) Sensitivity analysis of  $\Delta T_{\max}$  for the same device, with respect to the expected thermal conductivity ( $k$ ) range of  $\text{Al}_2\text{O}_3$ , Ni, and ITO. (c) Sensitivity analysis of  $\Delta T_{\max}$  with respect to TBC at material interfaces, showing minimal dependence on TBC at ITO-Ni, ITO- $\text{Al}_2\text{O}_3$ , and Ni- $\text{Al}_2\text{O}_3$  interfaces. However,  $\Delta T_{\max}$  varies with the TBC of ITO- $\text{SiO}_2$  interface, estimated to be  $35 \pm 12 \text{ MWm}^{-2}\text{K}^{-1}$  by comparing to the SThM measurements. (d) Dependence of  $\Delta T_{\max}$  on input power,  $P$ . Filled symbols mark SThM-measured temperature, hollow symbol is a simulation of  $\Delta T_{\max}$  at  $P_{\text{BD,avg}}$  from in Figure 3d. Dashed line is a linear fit, to highlight the trend. (e) Initial strain distribution ( $\varepsilon_{xx}$ ) along the 'x' white arrow in panel (a), showing tensile strain in the ITO channel and compressive strain under contacts (black curve). At device breakdown with self-heating, the compressive strain peaks at the channel/contact edge (red curve). (f) Summary of breakdown temperature ( $T_{\text{BD}}$ ) and peak compressive strain ( $|\varepsilon_{xx}|$ ) vs breakdown power for ITO transistors on 100 nm  $\text{SiO}_2$  and on 30 nm  $\text{HfO}_2$  dielectric, on Si back-gate.

is observed near the channel-contact edges and compressive strain appears under the contacts, which is attributed to the presence of Ni contacts.<sup>48</sup> (We report stress from a 80 nm evaporated Ni layer in Supporting Information Section S5.) With  $P_{\text{BD,avg}}$  input power the device self-heats and the mismatch in coefficient of thermal expansion (CTE,  $\alpha$ ) between ITO ( $\alpha_{\text{ITO}} \approx 8 \times 10^{-6} \text{ K}^{-1}$ )<sup>59,60</sup> and  $\text{SiO}_2$  ( $\alpha_{\text{SiO}_2} \approx 5.6 \times 10^{-7} \text{ K}^{-1}$ )<sup>61,62</sup> generates compressive strain at the channel edges (red lines in Figure 5e). The position of these compressive strain peaks corresponds to the locations of channel cracks seen in the SEM images from Figure 2e,f.

**Discussion and Comparison to ITO on  $\text{HfO}_2$ .** We note that the  $\sim 0.06\%$  compressive strain suggested by our device simulations is lower than typical crack onset strain (COS) values previously reported for ITO, which range from 0.1% to several percent.<sup>63–67</sup> Part of this may be due to nonuniformities in our devices and contacts (e.g., Ni contact grains or nonuniform current flow at high input power), which cannot be captured by simulations that assume uniform material properties. In addition, the COS is also expected to depend on ITO thickness, substrate, and deposition conditions, and most reported COS values were under externally applied mechanical stresses. In contrast, cracking of ultrathin ITO due to compressive strain induced by electrical self-heating has not been previously explored.

Our findings suggest that the cracking failure of these ultrathin ITO transistors on  $\text{SiO}_2$  is caused by the CTE mismatch between ITO and  $\text{SiO}_2$ , and initiated by self-heating effects during device operation. This CTE mismatch generates compressive strain near the channel edges, which appears to

exceed the reduced COS of the ITO material at the elevated temperature. We also note that the low crystallization temperature of ITO ( $\sim 150$ – $200$  °C)<sup>63,64,68–71</sup> may accelerate structural changes during device self-heating, such as grain boundary formation and localized (e.g., filamentary) crystallization.<sup>10</sup> A previous study<sup>64</sup> also suggested that defects and grain boundaries, often introduced during low-temperature annealing, can act as stress concentrators, accelerating crack formation. These microstructural changes, coupled with thermal and electrical stresses, likely create a cascading effect that weakens the ITO channel and promotes crack formation. While our SEM images and finite-element modeling provide insights into crack formation, transmission electron microscopy (TEM) analysis could further elucidate the crack propagation mechanisms for nanoscale devices and is recommended for future studies.

For comparison, we also fabricated sputtered ITO transistors on 30 nm  $\text{HfO}_2$  on Si ( $p^{++}$ ) substrates, with more details provided in Supporting Information Section S6. Electrical and SThM characterizations, along with finite-element simulations, were performed following the same methodology as described in Figures 4 and 5. The thermal boundary conductance (TBC) at the ITO- $\text{HfO}_2$  interface was  $51 \pm 14 \text{ MWm}^{-2}\text{K}^{-1}$ , a value not previously available in the literature. While this  $\text{TBC}_{\text{ITO-HfO}_2}$  value is nearly 50% higher than the  $\text{TBC}_{\text{ITO-SiO}_2}$ , it still falls on the lower end of typical TBC values for material interfaces.<sup>20,72–74</sup> SThM measurements and simulations (Supporting Information Section S6) further revealed that the breakdown temperature of ITO transistors on 30 nm  $\text{HfO}_2$  lies between 292 and 340 °C, nearly double the  $T_{\text{BD}}$  of ITO

transistors on 100 nm  $\text{SiO}_2$  substrate (both on Si). Despite the higher  $T_{\text{BD}}$ , the maximum compressive strain at device breakdown was estimated to be only  $\sim 0.086\%$ , attributed to the closer CTE matching between ITO ( $\alpha_{\text{ITO}} \approx 8 \times 10^{-6} \text{ K}^{-1}$ ) and  $\text{HfO}_2$  ( $\alpha_{\text{HfO}_2} \approx 6 \times 10^{-6} \text{ K}^{-1}$ ).<sup>75,76</sup> Figure 5f highlights these differences by summarizing the  $T_{\text{BD}}$  and peak compressive strain ( $|\epsilon_{xx}|$ ) at the breakdown power for ITO transistors on both substrates.

These findings suggest that sputtered ITO transistors on 30 nm  $\text{HfO}_2$  have better heat dissipation and reduced thermal stress, enabling them to sustain higher power before breakdown. These results highlight the importance of efficient heat dissipation and CTE matching<sup>77</sup> in optimizing material systems for high-performance ITO transistors. Finally, as an additional comparison, we have also examined several ITO transistors prepared by atomic layer deposition (ALD), and observed similar breakdown behavior. Further details can be found in Supporting Information Section S7, where we also discuss how our findings could be extended to other amorphous oxide semiconductors.

## CONCLUSIONS

We investigated the high-field breakdown of ITO transistors using an electro-thermo-mechanical multiphysics approach. Comparing scanning thermal microscopy measurements with simulations, we obtained the steady-state device temperature and estimated the thermal boundary conductance (TBC) at the ITO- $\text{SiO}_2$  interface,  $35 \pm 12 \text{ MW m}^{-2} \text{ K}^{-1}$ . This relatively low TBC, combined with the significant mismatch in coefficient of thermal expansion (CTE) between ITO and  $\text{SiO}_2$ , induces compressive strain near the contacts during device operation and leads to breakdown. It is also possible that the low crystallization temperature of ITO amplifies microstructural changes, such as grain boundary formation, and further accelerates failure under thermal and electrical stress. For comparison, we also fabricated ITO transistors on 30 nm  $\text{HfO}_2$ , on the same Si back-gate substrates. The ITO- $\text{HfO}_2$  TBC is found to be  $51 \pm 14 \text{ MW m}^{-2} \text{ K}^{-1}$ , approximately 50% higher than for ITO- $\text{SiO}_2$ , which, combined with the thinner dielectric and closer CTE matching to ITO, enabled higher device breakdown power and temperature. This study provides insights into the electro-thermo-mechanical behavior of indium-based amorphous oxide transistors, underscoring the importance of heat dissipation and thermal stress management for their applications.

## METHODS

**Device Fabrication.** The fabrication began with either a thermally grown 100 nm  $\text{SiO}_2$  layer or a plasma-enhanced atomic layer deposited (PEALD) 30 nm  $\text{HfO}_2$  layer, both on  $p^{++}$  Si substrates, which also serve as back-gates. Next, the 4 nm amorphous indium tin oxide (ITO) channel was deposited at room temperature using AJA magnetron sputtering, under a base pressure of  $2 \times 10^{-8}$  Torr or lower. ITO was RF-sputtered at 100 W in a 5 mTorr argon–oxygen (5:1) atmosphere, with a deposition rate of 9.6 Å/min. The ITO channel was then patterned by optical lithography (Heidelberg MLA150) and wet etching in a 1.7% HCl solution. Finally, nickel (Ni) contacts were deposited using a Kurt J. Lesker electron-beam evaporator, with a base pressure of  $\sim 5 \times 10^{-8}$  Torr and a deposition rate of 1 Å/s, patterned by lift-off.

**Electrical Characterization.** Electrical measurements were performed using a Keithley 4200 parameter analyzer with a Cascade Summit probe station, in air and room temperature ambient. Transfer curves ( $I_D$  vs  $V_{\text{GS}}$ ) were measured for over 90 devices by sweeping  $V_{\text{GS}}$

while keeping  $V_{\text{DS}} = 0.1$  V. Breakdown measurements were conducted on a subset of 10 devices for each  $V_{\text{GS}}$ , sweeping  $V_{\text{DS}}$  from 0 to 40 V. Scanning electron microscopy (SEM) images were taken with a Thermo Fisher Apreo SEM to examine devices after breakdown. Device transfer curves after breakdown were also measured.

**Thermal Characterization.** Prior to scanning thermal microscopy (SThM) measurements, devices were capped with a 6 nm  $\text{Al}_2\text{O}_3$  layer deposited via plasma-enhanced atomic layer deposition at 200 °C. The temperature rises of ITO transistors were measured using SThM, consisting of a commercial module from Anasys Instruments integrated with the MFP-3D AFM from Asylum Research. All measurements were performed in passive mode, where the sample was heated by electrical biasing. The SThM tip recorded temperature-dependent changes in its electrical resistance, and produce a voltage signal ( $V_{\text{SThM}}$ ), which was then converted to a temperature rise ( $\Delta T$ ) through a calibration process listed in Supporting Information Section S3. The SThM scans were conducted in contact mode at a set point of 0.5 V and a scan rate of 0.8 Hz. Measurements were performed at room temperature ( $\sim 20$  °C) in air under 20–30% humidity. The thermal probe used in this work (PR-EX-GLA-S, from Anasys Instruments) is made of a thin Pd layer on SiN.

**Finite-Element Modeling.** The finite-element electro-thermo-mechanical simulations were conducted using COMSOL Multiphysics. Steady-state simulations were conducted with the bottom of the Si substrate set as thermal ground. The ITO channel was modeled with a uniform sheet resistance across its width. We used nominal thermal conductivity ( $k$ ) and thermal boundary conductance ( $G$ ) values as listed in Supporting Information Table S1. Some  $G$  values not available in literature were approximated by values for pairs of similar and/or better-studied materials. Sensitivity analysis was carried out by varying  $k$  and  $G$  values to understand their impact. In addition, the strain distribution in ITO transistors during operation was assessed using the COMSOL thermal expansion model, with mechanical properties listed in Supporting Information Table S2. The initial strain induced by Ni contact was assessed by wafer-level Ni stress characterization, with further details provided in Supporting Information Section S5.

## ASSOCIATED CONTENT

### Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acsnano.5c01572>.

Fabrication process flow (Section S1), additional electrical breakdown characteristics (Section S2), scanning thermal microscopy details (Section S3), finite-element electro-thermo-mechanical modeling (Section S4), wafer-scale Ni stress characterization (Section S5), devices on 30 nm  $\text{HfO}_2$  dielectric (Section S6), and breakdown behavior of ALD-grown ITO devices (Section S7) ([PDF](#))

## AUTHOR INFORMATION

### Corresponding Author

Eric Pop – Department of Electrical Engineering, Department of Materials Science and Engineering, Department of Applied Physics, and Precourt Institute for Energy, Stanford University, Stanford, California 94305, United States;

ORCID: [0000-0003-0436-8534](https://orcid.org/0000-0003-0436-8534); Email: [epop@stanford.edu](mailto:epop@stanford.edu)

## Authors

**Haotian Su** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0009-0002-7113-0390](https://orcid.org/0009-0002-7113-0390)

**Yuan-Mau Lee** — Department of Materials Science and Engineering, Stanford University, Stanford, California 94305, United States

**Tara Peña** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States

**Sydney Fultz-Waters** — Department of Materials Science and Engineering, Stanford University, Stanford, California 94305, United States

**Jimin Kang** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States

**Çağrı Körülü** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0002-2701-9241](https://orcid.org/0000-0002-2701-9241)

**Sumaiya Wahid** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-1561-2627](https://orcid.org/0000-0003-1561-2627)

**Christina J. Newcomb** — Stanford Nano Shared Facilities, Stanford University, Stanford, California 94305, United States

**Young Suh Song** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States

**H.-S. Philip Wong** — Department of Electrical Engineering, Stanford University, Stanford, California 94305, United States

**Shan X. Wang** — Department of Electrical Engineering and Department of Materials Science and Engineering, Stanford University, Stanford, California 94305, United States

Complete contact information is available at:

<https://pubs.acs.org/10.1021/acsnano.5c01572>

## Author Contributions

H.S. and Y.L. contributed equally to this work. H.S. and Y.L. designed the experiments, supported by E.P. H.S. and Y.L. fabricated the samples and performed electrical characterization with support from T.P., J.K., and S.W. H.S. performed SThM measurements and conducted finite-element simulations with input from S.F.-W., Ç.K., and E.P. H.S. wrote the initial manuscript, with input from Y.L. and E.P. All authors discussed the results and edited the manuscript.

## Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

Several authors were supported by PRISM and SUPREME, JUMP 2.0 centers sponsored by the Semiconductor Research Corporation (SRC) and DARPA. This work was also supported in part by the National Science Foundation under Grant No. 2345655 in the Partnerships for Innovation (PFI) program. The authors also acknowledge partial support from the Stanford Nonvolatile Memory Technology Research Initiative (NMTRI) Affiliates program. Part of this work was performed at Stanford Nanofabrication Facility (SNF) and Stanford Nano Shared Facilities (SNSF), supported by the National Science Foundation under award ECCS-2026822.

## REFERENCES

- (1) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. *Nature* **2004**, *432* (7016), 488–492.

- (2) Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. *Npg Asia Mater.* **2010**, *2* (1), 15–22.

- (3) Park, J. S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. *Thin Solid Films* **2012**, *S20* (6), 1679–1693.

- (4) Hikake, K.; Li, Z.; Hao, J.; Pandy, C.; Saraya, T.; Hiramoto, T.; Takahashi, T.; Uenuma, M.; Uraoka, Y.; Kobayashi, M. A Nanosheet Oxide Semiconductor FET Using ALD InGaO<sub>x</sub> Channel and InSnO<sub>x</sub> Electrode with Normally-off Operation, High Mobility and Reliability for 3D Integrated Devices. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2023.

- (5) Liu, S.; Jana, K.; Toprasertpong, K.; Chen, J.; Liang, Z.; Jiang, Q.; Wahid, S.; Qin, S.; Chen, W.-C.; Wong, H. S. P. Gain Cell Memory on Logic Platform—Device Guidelines for Oxide Semiconductor Transistor Materials Development. In 2023 International Electron Devices Meeting (IEDM), 2023.

- (6) Li, S.; Tian, M.; Gao, Q.; Wang, M.; Li, T.; Hu, Q.; Li, X.; Wu, Y. Nanometre-thin indium tin oxide for advanced high-performance electronics. *Nat. Mater.* **2019**, *18* (10), 1091–1097.

- (7) Toprasertpong, K.; Liu, S.; Chen, J.; Wahid, S.; Jana, K.; Chen, W.-C.; Li, S.; Pop, E.; Wong, H. S. P. Co-designed Capacitive Coupling-Immune Sensing Scheme for Indium-Tin-Oxide (ITO) 2T Gain Cell Operating at Positive Voltage Below 2 V. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2023.

- (8) Wahid, S.; Daus, A.; Kumar, A.; Wong, H. S. P.; Pop, E. First Demonstration of Dual-Gated Indium Tin Oxide Transistors with Record Drive Current  $\sim 2.3$  mA/ $\mu$ m at  $L \approx 60$  nm and  $V_{DS} = 1$  V. In 2022 International Electron Devices Meeting (IEDM), 2022.

- (9) Wahid, S.; Daus, A.; Kwon, J.; Qin, S.; Ko, J.-S.; Wong, H. S. P.; Pop, E. Effect of Top-Gate Dielectric Deposition on the Performance of Indium Tin Oxide Transistors. *IEEE Electron Device Lett.* **2023**, *44* (6), 951–954.

- (10) Hu, Q.; Gu, C.; Liu, S.; Zeng, M.; Zhu, S.; Kang, J.; Liu, R.; Zhao, W.; Tong, A.; Li, Q.; et al. First Demonstration of Top-Gate Indium-Tin-Oxide RF Transistors with Record High Cut-off Frequency of 48 GHz,  $Id$  of 2.32 mA/ $\mu$ m and  $gm$  of 900  $\mu$ S/ $\mu$ m on SiC Substrate with Superior Reliability at 85 °C. In 2023 International Electron Devices Meeting (IEDM), 2023.

- (11) Urakawa, S.; Tomai, S.; Ueoka, Y.; Yamazaki, H.; Kasami, M.; Yano, K.; Wang, D.; Furuta, M.; Horita, M.; Ishikawa, Y.; et al. Thermal analysis of amorphous oxide thin-film transistor degraded by combination of joule heating and hot carrier effect. *Appl. Phys. Lett.* **2013**, *102* (5), 053506.

- (12) Liao, P.-Y.; Alajlouni, S.; Si, M.; Zhang, Z.; Lin, Z.; Noh, J.; Wilk, C.; Shakouri, A.; Ye, P. D. Thermal Studies of BEOL-compatible Top-Gated Atomically Thin ALD In<sub>2</sub>O<sub>3</sub> FETs. In 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), 2022.

- (13) Liao, P.-Y.; Khot, K.; Alajlouni, S.; Snure, M.; Noh, J.; Si, M.; Zhang, Z.; Shakouri, A.; Ruan, X.; Ye, P. D. Alleviation of Self-Heating Effect in Top-Gated Ultrathin In<sub>2</sub>O<sub>3</sub> FETs Using a Thermal Adhesion Layer. *IEEE Trans. Electron Devices* **2023**, *70* (1), 113–120.

- (14) Liao, P.-Y.; Zheng, D.; Alajlouni, S.; Zhang, Z.; Si, M.; Zhang, J.; Lin, J.-Y.; Feygelson, T. I.; Tadjer, M. J.; Shakouri, A.; et al. Transient Thermal and Electrical Co-Optimization of BEOL Top-Gated ALD In<sub>2</sub>O<sub>3</sub> FETs Toward Monolithic 3-D Integration. *IEEE Trans. Electron Devices* **2023**, *70* (4), 2052–2058.

- (15) Charnas, A.; Zhang, Z.; Lin, Z.; Zheng, D.; Zhang, J.; Si, M.; Ye, P. D. Review—Extremely Thin Amorphous Indium Oxide Transistors. *Adv. Mater.* **2024**, *36* (9), e2304044.

- (16) Sabry Aly, M. M.; Gao, M.; Hills, G.; Lee, C.-S.; Pitner, G.; Shulaker, M. M.; Wu, T. F.; Asheghi, M.; Bokor, J.; Franchetti, F.,

et al. Energy-Efficient Abundant-Data Computing: The N3XT 1,000x. *Computer* **2015**, *48* (12), 24–33.

(17) Srimani, T.; Bechdolt, A.; Choi, S.; Gilardi, C.; Kasperovich, A.; Li, S.; Lin, Q.; Malakoutian, M.; McEwen, P.; Radway, R. M.; et al. *N3XT 3D Technology Foundations and Their Lab-to-Fab: Omni 3D Logic, Logic+Memory Ultra-Dense 3D, 3D Thermal Scaffolding*. In 2023 International Electron Devices Meeting (IEDM), 2023.

(18) Wong, H. S. P.; Akarvardar, K.; Antoniadis, D.; Bokor, J.; Hu, C.; King-Liu, T.-J.; Mitra, S.; Plummer, J. D.; Salahuddin, S. A Density Metric for Semiconductor Technology [Point of View]. *Proceedings of the IEEE* **2020**, *108* (4), 478–482.

(19) Zhang, Y.; Sarvey, T. E.; Bakir, M. S. *Thermal challenges for heterogeneous 3D ICs and opportunities for air gap thermal isolation*. In 2014 International 3D Systems Integration Conference (3DIC), 2014.

(20) Pop, E. Energy dissipation and transport in nanoscale devices. *Nano Res.* **2010**, *3* (3), 147–169.

(21) Li, W.; Gong, X.; Yu, Z.; Ma, L.; Sun, W.; Gao, S.; Koroglu, C.; Wang, W.; Liu, L.; Li, T.; et al. Approaching the quantum limit in two-dimensional semiconductor contacts. *Nature* **2023**, *613* (7943), 274–279.

(22) Shin, S.; Wahab, M. A.; Masuduzzaman, M.; Maize, K.; Gu, J.; Si, M.; Shakouri, A.; Ye, P. D.; Alam, M. A. Direct Observation of Self-Heating in III–V Gate-All-Around Nanowire MOSFETs. *IEEE Trans. Electron Devices* **2015**, *62* (11), 3516–3523.

(23) Su, H.; Kwon, H.; Hwang, W.; Xue, F.; Körögülu, Ç.; Tsai, W.; Asheghi, M.; Goodson, K. E.; Wang, S. X.; Pop, E. Thermal optimization of two-terminal SOT-MRAM. *J. Appl. Phys.* **2024**, *136* (1), 013901.

(24) Van Beek, S.; Cai, K.; Rao, S.; Jayakumar, G.; Couet, S.; Jossart, N.; Chasin, A.; Kar, G. S. *MTJ degradation in SOT-MRAM by self-heating-induced diffusion*. In 2022 IEEE International Reliability Physics Symposium (IRPS), 2022.

(25) Sturm, J. C.; Wilson, W.; Iodice, H. Thermal effects and scaling in organic light-emitting flat-panel displays. *IEEE J. Sel. Top. Quantum Electron.* **1998**, *4* (1), 75–82.

(26) Kirch, A.; Fischer, A.; Liero, M.; Fuhrmann, J.; Glitzky, A.; Reineke, S. Experimental proof of Joule heating-induced switched-back regions in OLEDs. *Light Sci. Appl.* **2020**, *9*, 5.

(27) Azrain, M. M.; Mansor, M. R.; Omar, G.; Fadzullah, S. H. S. M.; Esa, S. R.; Lim, L. M.; Sivakumar, D.; Nordin, M. N. A. Effect of high thermal stress on the organic light emitting diodes (OLEDs) performances. *Synth. Met.* **2019**, *247*, 191–201.

(28) Körögülu, Ç.; Pop, E. High Thermal Conductivity Insulators for Thermal Management in 3D Integrated Circuits. *IEEE Electron Device Lett.* **2023**, *44* (3), 496–499.

(29) Gabourie, A. J.; Polanco, C. A.; McClellan, C. J.; Su, H.; Malakoutian, M.; Körögülu, Ç.; Chowdhury, S.; Donadio, D.; Pop, E. *AI-Accelerated Atoms-to-Circuits Thermal Simulation Pipeline for Integrated Circuit Design*. In 2024 IEEE International Electron Devices Meeting (IEDM), 2024.

(30) Diaz, C. H. *Logic Technology Device Innovations*. In 2024 IEEE International Electron Devices Meeting (IEDM), 2024.

(31) Xia, F.; Xia, T.; Su, H.; Gan, L.; Hu, Q.; Wang, W.; Huang, R.; Bai, T.; Chen, Y.; Ma, C.; et al. Flexible radio-frequency transistors exceeding 100 GHz. 2025; p arXiv:2502.02485.

(32) Daus, A.; Vaziri, S.; Chen, V.; Körögülu, Ç.; Grady, R. W.; Bailey, C. S.; Lee, H. R.; Schauble, K.; Brenner, K.; Pop, E. High-performance flexible nanoscale transistors based on transition metal dichalcogenides. *Nat. Electron.* **2021**, *4* (7), 495–501.

(33) Besleaga, C.; Stan, G. E.; Pintilie, I.; Barquinha, P.; Fortunato, E.; Martins, R. Transparent field-effect transistors based on AlN-gate dielectric and IGZO-channel semiconductor. *Appl. Surf. Sci.* **2016**, *379*, 270–276.

(34) Kise, K.; Fujii, M. N.; Bermundo, J. P.; Ishikawa, Y.; Uraoka, Y. Self-Heating Suppressed Structure of a-IGZO Thin-Film Transistor. *IEEE Electron Device Lett.* **2018**, *39* (9), 1322–1325.

(35) Lin, J. Y.; Zhang, Z.; Alajlouni, S.; Liao, P. Y.; Lin, Z.; Niu, C.; Shakouri, A.; Ye, P. D. *First Determination of Thermal Resistance and Thermal Capacitance of Atomic-Layer-Deposited  $In_2O_3$  Transistors*. In 2023 International Electron Devices Meeting (IEDM), 2023.

(36) Gabourie, A. J.; Körögülu, Ç.; Pop, E. Substrate-dependence of monolayer  $MoS_2$  thermal conductivity and thermal boundary conductance. *J. Appl. Phys.* **2022**, *131* (19), 195103.

(37) Yalon, E.; McClellan, C. J.; Smithe, K. K. H.; Munoz Rojo, M.; Xu, R. L.; Suryavanshi, S. V.; Gabourie, A. J.; Neumann, C. M.; Xiong, F.; Farimani, A. B.; et al. Energy Dissipation in Monolayer  $MoS_2$  Electronics. *Nano Lett.* **2017**, *17* (6), 3429–3433.

(38) Huang, J.; Li, Y.; Yu, X.; Liu, Z.; Wang, F.; Yue, Y.; Zhang, R.; Dai, R.; Yang, K.; Liu, H.; et al. Improved Thermal Dissipation in a  $MoS_2$  Field-Effect Transistor by Hybrid High-k Dielectric Layers. *ACS Appl. Mater. Interfaces* **2024**, *16* (45), 62527–62536.

(39) Jiang, P.; Qian, X.; Yang, R. Tutorial: Time-domain thermoreflectance (TDTR) for thermal property characterization of bulk and thin film materials. *J. Appl. Phys.* **2018**, *124* (16), 161103.

(40) Kwon, H.; Perez, C.; Park, W.; Asheghi, M.; Goodson, K. E. Thermal Characterization of Metal-Oxide Interfaces Using Time-Domain Thermoreflectance with Nanograting Transducers. *ACS Appl. Mater. Interfaces* **2021**, *13* (48), 58059–58065.

(41) Su, H.; Kwon, H.; Xue, F.; Sato, N.; Bhat, U.; Tsai, W.; Bosman, M.; Asheghi, M.; Goodson, K. E.; Pop, E.; et al. Thermal Characterization of Ultrathin  $MgO$  Tunnel Barriers. *Nano Lett.* **2024**, *24* (46), 14567–14573.

(42) Zhang, Y.; Zhu, W.; Hui, F.; Lanza, M.; Borca-Tasciuc, T.; Muñoz Rojo, M. A Review on Principles and Applications of Scanning Thermal Microscopy (SThM). *Adv. Funct. Mater.* **2020**, *30* (18), 1900892.

(43) Swoboda, T.; Wainstein, N.; Deshmukh, S.; Koroglu, C.; Gao, X.; Lanza, M.; Hilgenkamp, H.; Pop, E.; Yalon, E.; Munoz Rojo, M. Nanoscale temperature sensing of electronic devices with calibrated scanning thermal microscopy. *Nanoscale* **2023**, *15* (15), 7139–7146.

(44) Datye, I. M.; Rojo, M. M.; Yalon, E.; Deshmukh, S.; Mleczko, M. J.; Pop, E. Localized Heating and Switching in  $MoTe_2$ -Based Resistive Memory Devices. *Nano Lett.* **2020**, *20* (2), 1461–1467.

(45) Deshmukh, S.; Rojo, M. M.; Yalon, E.; Vaziri, S.; Koroglu, C.; Islam, R.; Iglesias, R. A.; Saraswat, K.; Pop, E. Direct measurement of nanoscale filamentary hot spots in resistive memory devices. *Sci. Adv.* **2022**, *8* (13), eabk1514.

(46) Yalon, E.; Deshmukh, S.; Munoz Rojo, M.; Lian, F.; Neumann, C. M.; Xiong, F.; Pop, E. Spatially Resolved Thermometry of Resistive Memory Devices. *Sci. Rep.* **2017**, *7* (1), 15360.

(47) Jaikissoon, M.; Körögülu, Ç.; Yang, J. A.; Neilson, K.; Saraswat, K. C.; Pop, E. CMOS-compatible strain engineering for monolayer semiconductor transistors. *Nat. Electron.* **2024**, *7* (10), 885–891.

(48) Hoang, L.; Jaikissoon, M.; Koroglu, C.; Zhang, Z.; Bennett, R. K. A.; Song, J. H.; Yang, J. A.; Ko, J. S.; Brongersma, M. L.; Saraswat, K. C.; et al. Understanding the Impact of Contact-Induced Strain on the Electrical Performance of Monolayer  $WS_2$  Transistors. *Nano Lett.* **2024**, *24* (41), 12768–12774.

(49) Polonsky, S.; Jenkins, K. A. Time-Resolved Measurements of Self-Heating in SOI and Strained-Silicon MOSFETs Using Photon Emission Microscopy. *IEEE Electron Device Lett.* **2004**, *25* (4), 208–210.

(50) Beppu, N.; Oda, S.; Uchida, K. *Experimental study of self-heating effect (SHE) in SOI MOSFETs: Accurate understanding of temperatures during AC conductance measurement, proposals of  $2\omega$  method and modified pulsed IV*. In 2012 International Electron Devices Meeting, 2012.

(51) Makovejev, S.; Olsen, S. H.; Kilchytska, V.; Raskin, J.-P. Time and Frequency Domain Characterization of Transistor Self-Heating. *IEEE Trans. Electron Devices* **2013**, *60* (6), 1844–1851.

(52) Islam, S.; Li, Z.; Dorgan, V. E.; Bae, M.-H.; Pop, E. Role of Joule Heating on Current Saturation and Transient Behavior of Graphene Transistors. *IEEE Electron Device Lett.* **2013**, *34* (2), 166–168.

(53) Deng, S.; Kwak, J.; Lee, J.; Aabrar, K. A.; Kim, T.-H.; Choe, G.; Kirtania, S. G.; Zhang, C.; Li, W.; Phadke, O.; et al. *BEOL Compatible Oxide Power Transistors for On-Chip Voltage Conversion in*

Heterogenous 3D (H3D) Integrated Circuits. In 2023 International Electron Devices Meeting (IEDM), 2023.

(54) Wu, W.; Huang, T.; Yang, G.; Cao, J.; Yu, Z.; Sun, H.; Xu, Y.; Sun, W. High-Voltage Indium-Tin-Oxide Thin-Film Transistors Possessing Drift Region Capped With Indium-Tin-Oxide Layer. *IEEE Electron Device Lett.* **2024**, *45* (7), 1201–1204.

(55) Xie, J.; Wang, Y.; Zheng, Z.; Kang, Y.; Chen, X.; Zheng, G.; Shao, R.; Han, K.; Gong, X. Top-Gate Indium-Tin-Oxide Power Transistors Featuring High Breakdown Voltage of 156 V. *IEEE Electron Device Lett.* **2024**, *45* (10), 1847–1850.

(56) Yang, H.; Huang, T.; Pan, W.; Lu, L.; Zhang, S. Output breakdown characteristics of amorphous InGaZnO thin-film transistors at high gate voltage. *Appl. Phys. Lett.* **2024**, *124*, 093501.

(57) Smithe, K. K. H.; English, C. D.; Suryavanshi, S. V.; Pop, E. High-Field Transport and Velocity Saturation in Synthetic Monolayer MoS<sub>2</sub>. *Nano Lett.* **2018**, *18* (7), 4516–4522.

(58) Feng, T.; Zhou, H.; Cheng, Z.; Larkin, L. S.; Neupane, M. R. A Critical Review of Thermal Boundary Conductance across Wide and Ultrawide Bandgap Semiconductor Interfaces. *ACS Appl. Mater. Interfaces* **2023**, *15* (25), 29655–29673.

(59) Choi, S. K.; Lee, J. I. Effect of film density on electrical properties of indium tin oxide films deposited by dc magnetron reactive sputtering. *Journal of Vacuum Science & Technology A: Vacuum, Surfaces, and Films* **2001**, *19* (5), 2043–2047.

(60) Krataithong, C.; Srichai, K.; Wongrat, E.; Tubtimtae, A. Comparative study on the influence of transparent glass substrates for antimony telluride thin films via structural and optical properties. *Journal of Science: Advanced Materials and Devices* **2022**, *7* (3), 100449.

(61) El-Kareh, B. *Fundamentals of Semiconductor Processing Technology*; Springer, 1995. ISBN 13:9781461522096.

(62) Luo, S.; Cullen, C. P.; Guo, G.; Zhong, J.; Duesberg, G. S. Investigation of growth-induced strain in monolayer MoS<sub>2</sub> grown by chemical vapor deposition. *Appl. Surf. Sci.* **2020**, *508*, 145126.

(63) Leterrier, Y.; Médico, L.; Demarco, F.; Månsen, J. A. E.; Betz, U.; Escolà, M. F.; Kharrazi Olsson, M.; Atamny, F. Mechanical integrity of transparent conductive oxide films for flexible polymer-based displays. *Thin Solid Films* **2004**, *460*, 156–166.

(64) Oh, S. J.; Kwon, J. H.; Lee, S.; Choi, K. C.; Kim, T. S. Unveiling the Annealing-Dependent Mechanical Properties of Freestanding Indium Tin Oxide Thin Films. *ACS Appl. Mater. Interfaces* **2021**, *13* (14), 16650–16659.

(65) Zhou, J.; Zhang, X.; Zhang, X.; Zhang, W.; Li, J.; Chen, Y.; Liu, H.; Yan, Y. Mechanical Properties of Tensile Cracking in Indium Tin Oxide Films on Polycarbonate Substrates. *Coatings* **2022**, *12* (4), 538.

(66) Hengst, C.; Menzel, S. B.; Rane, G. K.; Smirnov, V.; Wilken, K.; Leszczynska, B.; Fischer, D.; Prager, N. Mechanical Properties of ZTO, ITO, and a-Si:H Multilayer Films for Flexible Thin Film Solar Cells. *Materials (Basel)* **2017**, *10* (3), 245.

(67) Peng, C.; Jia, Z.; Bianculli, D.; Li, T.; Lou, J. In situ electro-mechanical experiments and mechanics modeling of tensile cracking in indium tin oxide thin films on polyimide substrates. *J. Appl. Phys.* **2011**, *109* (10), 103530.

(68) Kim, J.; Shrestha, S.; Souri, M.; Connell, J. G.; Park, S.; Seo, A. High-temperature optical properties of indium tin oxide thin-films. *Sci. Rep.* **2020**, *10* (1), 12486.

(69) Paine, D. C.; Whitson, T.; Janiac, D.; Beresford, R.; Yang, C. O.; Lewis, B. A study of low temperature crystallization of amorphous thin film indium–tin–oxide. *J. Appl. Phys.* **1999**, *85* (12), 8445–8450.

(70) Guillén, C.; Herrero, J. Polycrystalline growth and recrystallization processes in sputtered ITO thin films. *Thin Solid Films* **2006**, *510* (1–2), 260–264.

(71) Guillén, C.; Herrero, J. Structure, optical, and electrical properties of indium tin oxide thin films prepared by sputtering at room temperature and annealed in air or nitrogen. *J. Appl. Phys.* **2007**, *101* (7), 073514.

(72) Hopkins, P. E. Thermal Transport across Solid Interfaces with Nanoscale Imperfections: Effects of Roughness, Disorder, Dislocations, and Bonding on Thermal Boundary Conductance. *ISRN Mech. Eng.* **2013**, *2013*, 682586.

(73) Cahill, D. G.; Braun, P. V.; Chen, G.; Clarke, D. R.; Fan, S.; Goodson, K. E.; Kebinski, P.; King, W. P.; Mahan, G. D.; Majumdar, A.; et al. Nanoscale thermal transport. II. 2003–2012. *Appl. Phys. Rev.* **2014**, *1* (1), 011305.

(74) Monachon, C.; Weber, L.; Dames, C. Thermal Boundary Conductance: A Materials Science Perspective. *Annu. Rev. Mater. Res.* **2016**, *46*, 433.

(75) Gaskins, J. T.; Hopkins, P. E.; Merrill, D. R.; Bauers, S. R.; Hadland, E.; Johnson, D. C.; Koh, D.; Yum, J. H.; Banerjee, S.; Nordell, B. J.; et al. Review—Investigation and Review of the Thermal, Mechanical, Electrical, Optical, and Structural Properties of Atomic Layer Deposited High-k Dielectrics: Beryllium Oxide, Aluminum Oxide, Hafnium Oxide, and Aluminum Nitride. *ECS Journal of Solid State Science and Technology* **2017**, *6* (10), N189–N208.

(76) Gluch, J.; Rößler, T.; Menzel, S. B.; Eckert, J. Microstructure and stress in high-k Hf–Y–O thin films. *Microelectron. Eng.* **2011**, *88* (5), 561–563.

(77) Pradhan, D. K.; Moore, D. C.; Francis, A. M.; Kupernik, J.; Kennedy, W. J.; Glavin, N. R.; Olsson, R. H.; Jariwala, D. Materials for high-temperature digital electronics. *Nature Reviews Materials* **2024**, *9* (11), 790–807.

## SUPPORTING INFORMATION

# High-field Breakdown and Thermal Characterization of Indium Tin Oxide Transistors

Haotian Su<sup>1,†</sup>, Yuan-Mau Lee<sup>2,†</sup>, Tara Peña<sup>1</sup>, Sydney Fultz-Waters<sup>2</sup>, Jimin Kang<sup>1</sup>, Çağıl Köröḡlu<sup>1</sup>, Sumaiya Wahid<sup>1</sup>, Christina J. Newcomb<sup>3</sup>, Young Suh Song<sup>1</sup>, H.-S. Philip Wong<sup>1</sup>, Shan X. Wang<sup>1,2</sup>, and Eric Pop<sup>1,2,4,5,\*</sup>

<sup>1</sup>Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA

<sup>2</sup>Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305, USA

<sup>3</sup>Stanford Nano Shared Facilities, Stanford University, Stanford, CA 94305, USA

<sup>4</sup>Department of Applied Physics, Stanford University, Stanford, CA 94305, USA

<sup>5</sup>Precourt Institute for Energy, Stanford University, CA 94305, USA

<sup>†</sup>Authors contributed equally. \*Contact: [epop@stanford.edu](mailto:epop@stanford.edu)

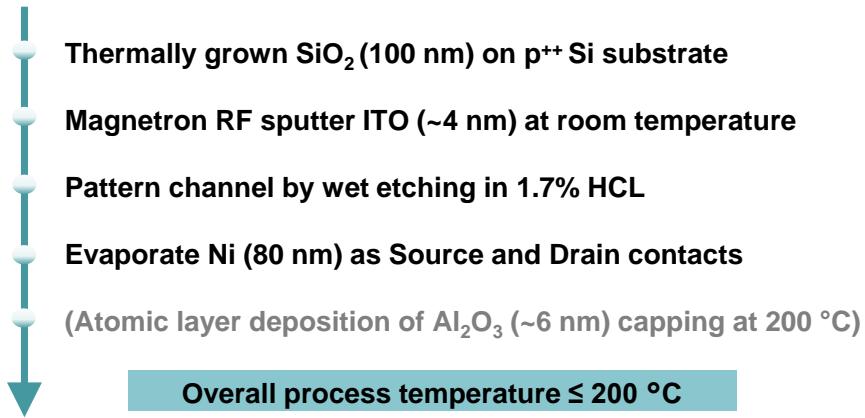

### S1. Fabrication Process Flow

The fabrication process flow is illustrated in **Figure S1** and additional details are provided in the **Methods** section (main text). The deposition rates for all steps were calibrated using X-ray reflectivity. For scanning thermal microscopy (SThM) measurements, the devices were capped with a 6 nm Al<sub>2</sub>O<sub>3</sub> layer deposited via plasma-enhanced atomic layer deposition at 200 °C.

**Figure S1.** Fabrication process flow for ITO transistors, highlighting key steps. The entire process was conducted at temperatures  $\leq 200$  °C.

### S2. Additional Electrical Breakdown Characteristics

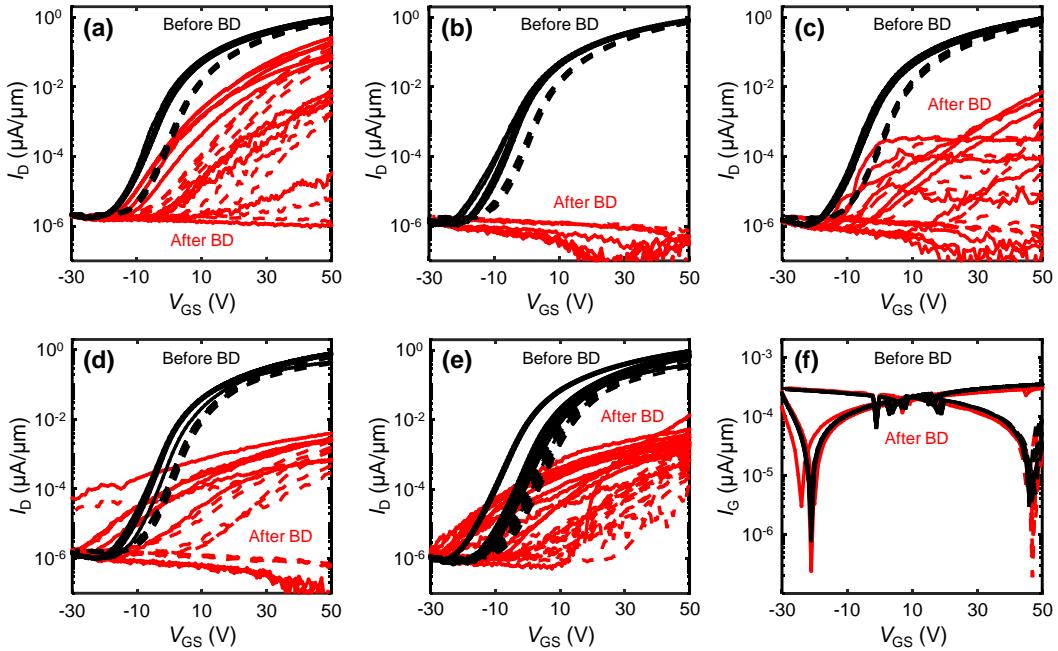

We conducted electrical breakdown measurements on ITO transistors under various biasing conditions; the transfer curves before and after breakdown are shown in **Figures S2a-e**. The transfer curves after breakdown under different breakdown biasing consistently exhibit a significant reduction in on-state  $I_D$  and loss of gate control. Gate leakage current ( $I_G$ ) was also monitored during all measurements and showed negligible change under breakdown conditions, as illustrated in **Figure S2f**. This suggests that the breakdown of ITO transistors is not due to gate dielectric breakdown.

**Figure S2.** Transfer curves ( $I_D$  vs.  $V_{GS}$ , measured at  $V_{DS} = 0.1$  V) of ITO transistors measured before (black) and after breakdown (red) under different breakdown biasing conditions: (a)  $V_{GS} = -15$  V and  $V_{DS} = 40$  V; (b)  $V_{GS} = 0$  V and  $V_{DS} = 40$  V; (c)  $V_{GS} = 15$  V and  $V_{DS} = 40$  V; (d)  $V_{GS} = 60$  V and  $V_{DS} = 40$  V; (e)  $V_{GS} = 75$  V and  $V_{DS} = 25$  V. Each figure displays  $\sim 10$  measured devices. Transfer curves after breakdown demonstrate a significant reduction in on-state  $I_D$  and loss of gate control. All devices have channel length of 1.6  $\mu\text{m}$ . Solid/dashed lines are forward/backward  $V_{GS}$  sweeps. (f) Gate leakage current ( $I_G$ ) vs.  $V_{GS}$  before (black) and after (red) breakdown under  $V_{GS} = 45$  V and  $V_{DS} = 40$  V, showing similar trends for both cases, which rules out gate dielectric breakdown as the failure mechanism. (Note the different vertical axis scale, compared to the other figure panels.)

### S3. Scanning Thermal Microscopy (SThM) Details

We measured the temperature rise of ITO transistors using scanning thermal microscopy (SThM). The SThM system employs a thermo-resistive probe connected to a Wheatstone bridge, a DC voltage source, and an amplifier specifically designed to minimize electrical spikes that could damage the probe.<sup>1-3</sup> The ITO transistors were capped with 6 nm  $\text{Al}_2\text{O}_3$  to prevent electrical shorting to the SThM probe. (Additional details are provided in the **Methods** section of the main text.) Although the SThM measures the surface temperature of this  $\text{Al}_2\text{O}_3$  rather than the underlying ITO channel, prior studies have shown that such thin capping layers have a negligible effect on the measurement,<sup>1,4</sup> because the surface temperature of the  $\text{Al}_2\text{O}_3$  layer closely matches the temperature of the ITO channel. To confirm this, we also conducted simulations with and without the capping layer, further verifying that the capping layer does not alter the temperature rise.

The SThM measurements produce a voltage signal ( $V_{\text{SThM}}$ ) that correlates with the sample surface temperature. To convert  $V_{\text{SThM}}$  to the corresponding temperature rise ( $\Delta T$ ), we previously calibrated the same SThM probes using samples with a set of Ti/Pd heaters of varying widths, as described by S. Deshmukh *et al.*<sup>3</sup> The conversion factor ( $F$ , with the unit of mV/K) is determined using the known temperature coefficient of resistance (TCR) of the metal lines. These heaters were capped with an  $\text{Al}_2\text{O}_3$  layer similar to that on our ITO transistors, to account for similar thermal

(boundary) resistance at the probe-sample interface. While the conversion factor ( $F$ ) can vary between probes, these variations are more obvious only for measurements on sub-200 nm features.<sup>3</sup> For the micron-scale ITO transistors in this study,  $F$  remains consistent across probes. Based on our calibration, we adopted a conversion factor  $F = 7.0 \pm 0.5$  mV/K for this study.

#### S4. Finite-element Electro-Thermo-Mechanical Modeling

We estimate the temperature rise ( $\Delta T$ , above room temperature) of our ITO transistors using three-dimensional finite-element electro-thermo-mechanical modeling, through COMSOL Multiphysics®.<sup>5</sup> To simplify the simulation, the ITO channel was modeled with a uniform sheet resistance across their width. Additionally, contact resistance is negligible in terms of heat generation because the ITO transistors in this study are sufficiently long<sup>6</sup> ( $L \approx 1.5$  to  $1.7$   $\mu\text{m}$ ). The thermal conductivity ( $k$ ) of the materials and thermal boundary conductance ( $G$ ) for various material interfaces used in our simulations are listed in **Table S1**.

**Table S1.** Nominal thermal properties used in simulations, including thermal conductivity ( $k$ ) and thermal boundary conductance ( $G$ ) values, all near room temperature. Some specific  $G$  values not available in the literature were approximated by  $G$  values for pairs of similar and/or better-studied materials.<sup>5</sup> The  $G$  of ITO-SiO<sub>2</sub> and ITO-HfO<sub>2</sub> were ultimately estimated to be  $35 \pm 12$  MWm<sup>-2</sup>K<sup>-1</sup> and  $51 \pm 14$  MWm<sup>-2</sup>K<sup>-1</sup>, respectively (see main text **Figure 5** and Supporting Information **Section S6**).

| Material                                        | $k$ (Wm <sup>-1</sup> K <sup>-1</sup> ) | Material Interface                 | $G$ (MWm <sup>-2</sup> K <sup>-1</sup> ) |

|-------------------------------------------------|-----------------------------------------|------------------------------------|------------------------------------------|

| p <sup>++</sup> Si <sup>1,7,8</sup>             | 95                                      | Si-SiO <sub>2</sub>                | 500                                      |

| SiO <sub>2</sub> <sup>9,10</sup>                | 1.4                                     | ITO-SiO <sub>2</sub>               | 50                                       |

| ITO <sup>11-15</sup>                            | 2                                       | ITO-Ni                             | 150                                      |

| Ni <sup>16,17</sup>                             | 40                                      | Ni-Al <sub>2</sub> O <sub>3</sub>  | 150                                      |

| Al <sub>2</sub> O <sub>3</sub> <sup>18,19</sup> | 1.5                                     | ITO-Al <sub>2</sub> O <sub>3</sub> | 50                                       |

| HfO <sub>2</sub> <sup>8,20-22</sup>             | 1.1                                     | Si-HfO <sub>2</sub>                | 283                                      |

|                                                 |                                         | ITO-HfO <sub>2</sub>               | 50                                       |

The assumption of  $2$  Wm<sup>-1</sup>K<sup>-1</sup> for the thermal conductivity of ITO, as well as the values for Al<sub>2</sub>O<sub>3</sub> and Ni, may not be entirely precise. To assess their impact, we carried out sensitivity analysis in **Figure 5b** of the main text, varying the thermal conductivity of ITO ( $1$ – $10$  Wm<sup>-1</sup>K<sup>-1</sup>), Al<sub>2</sub>O<sub>3</sub> ( $1.2$ – $3$  Wm<sup>-1</sup>K<sup>-1</sup>), and Ni ( $15$ – $60$  Wm<sup>-1</sup>K<sup>-1</sup>). The results show that these variations have a negligible effect on the device temperature rise during operation, within the typical power inputs used here, suggesting that our conclusions remain robust despite uncertainties in material properties. This is not surprising, because for our long-channel devices heat dissipation is “vertical” into the substrate, not “lateral” along the ITO and into the Ni contacts.

We estimate the electronic contribution to the ITO thermal conductivity with the Wiedemann-Franz law,  $k_e \approx 0.03$  Wm<sup>-1</sup>K<sup>-1</sup> at  $\sim 180$  °C, indicating that phonon transport dominates in our ultrathin ITO. Given this, we expect the total thermal conductivity of ITO to fall within the  $1$ – $10$  Wm<sup>-1</sup>K<sup>-1</sup> range, consistent with prior literature. The impact of Ni thermal conductivity is minimal, because our transistors are sufficiently long for heat dissipation to be dominated by the substrate rather than the contacts.<sup>23</sup> Similarly, even a  $\pm 20\%$  change in the thermal boundary conductance ( $G$ ) of Si-SiO<sub>2</sub> and Si-HfO<sub>2</sub> causes less than  $\pm 1\%$  change in the calculated ITO channel temperature rise ( $\Delta T$ ), because the dominant thermal resistance of our transistors is due to their underlying SiO<sub>2</sub> or HfO<sub>2</sub>. Sensitivity analysis of other  $G$  values is shown in the main text **Figure 5c**.

To investigate the strain distribution in ITO transistors during operation, we also conducted mechanical simulations by including the COMSOL thermal expansion module. The bottom of the Si substrate was set as the fixed boundary and linear elastic material properties were assumed for all constituent materials. The nominal mechanical properties, including the coefficient of thermal expansion ( $\alpha$ ), Young's modulus ( $E$ ), and Poisson's ratio ( $\nu$ ), are listed in **Table S2**. Additionally, the initial stress induced by the Ni layer was accounted for in the simulations, with further details provided in Supporting Information **Section S5**.

**Table S2.** Nominal mechanical properties used in simulations, including the coefficient of thermal expansion ( $\alpha$ ), Young's modulus ( $E$ ), and Poisson's ratio ( $\nu$ ) for constituent materials in the ITO transistor.

| Material                          | $\alpha$ (K <sup>-1</sup> ) | $E$ (GPa) | $\nu$ |

|-----------------------------------|-----------------------------|-----------|-------|

| SiO <sub>2</sub> <sup>24,25</sup> | $5.6 \times 10^{-7}$        | 70        | 0.17  |

| HfO <sub>2</sub> <sup>26,27</sup> | $6 \times 10^{-6}$          | 250       | 0.25  |

| ITO <sup>28-31</sup>              | $8 \times 10^{-6}$          | 250       | 0.33  |

| Ni <sup>32-35</sup>               | $1.3 \times 10^{-5}$        | 200       | 0.30  |

| Si <sup>24,25</sup>               | $2.6 \times 10^{-6}$        | 170       | 0.28  |

### S5. Wafer-scale Ni Stress Characterization

An 80 nm Ni layer was deposited via electron-beam evaporation onto a 350  $\mu$ m thick (100) Si wafer with native oxide, under a base pressure of  $\sim 5 \times 10^{-8}$  Torr. The wafer curvature was measured both before and after metal deposition. Using the Stoney equation,<sup>36</sup> the stress in the Ni film was found to be  $\sim 75$  MPa. The thin film force was also determined, defined as  $F = \sigma t$ , where  $\sigma$  is the film stress and  $t$  is the film thickness. The measured Ni thin film force, summarized in **Table S3**, align well with the values reported in the literature.<sup>37,38</sup>

**Table S3.** Extracted stress and thin film force for the 80 nm Ni layer deposited as metal contacts.

| Metal, nm | Stress (MPa) | Thin film force (N/m) |

|-----------|--------------|-----------------------|

| Ni, 80    | 75           | 6                     |

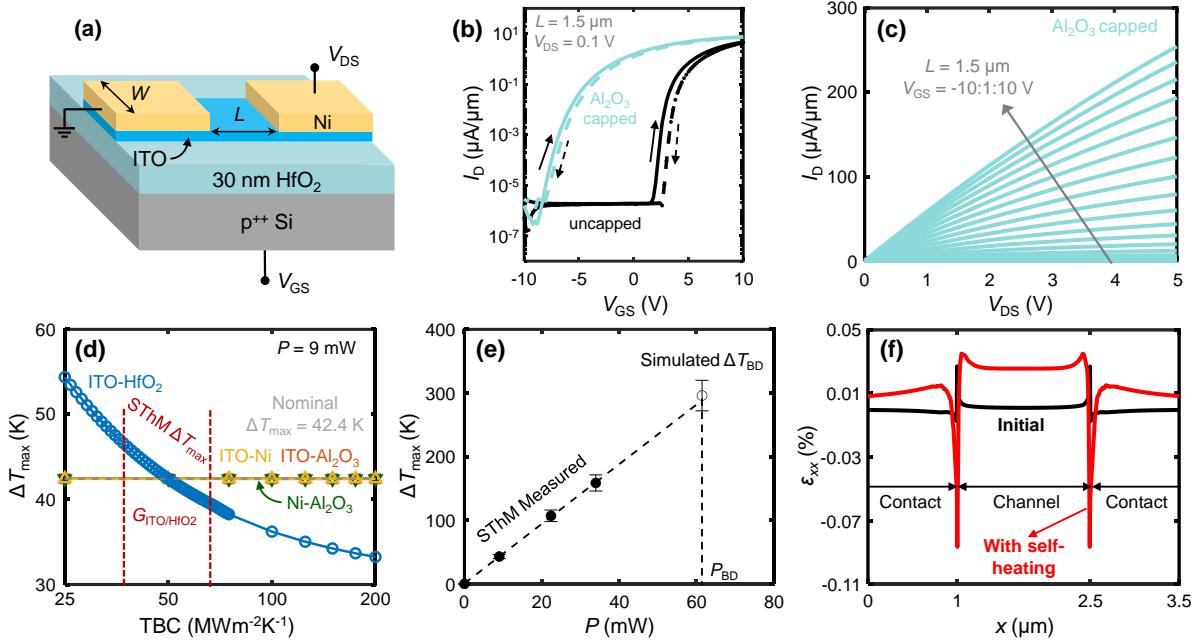

### S6. Devices on 30 nm HfO<sub>2</sub> Dielectric

We also fabricated sputtered ITO transistors on 30 nm HfO<sub>2</sub> back-gate dielectric on Si (p<sup>++</sup>) back-gate substrates, as shown in **Figure S3a**, using the same fabrication flow detailed in Supporting Information **Section S1**. The 30 nm HfO<sub>2</sub> layer was deposited by plasma-enhanced atomic layer deposition at 200 °C, and its thickness was calibrated by ellipsometry. Measured electrical transfer curves and output characteristics are shown in **Figures S3b-c**. The Al<sub>2</sub>O<sub>3</sub> capping layer was found to induce a negative shift in the threshold voltage, consistent with our previous study.<sup>6</sup> Combing SThM and finite-element simulations, we determined the TBC between the ITO channel and the HfO<sub>2</sub> dielectric to be  $51 \pm 14$  MWm<sup>-2</sup>K<sup>-1</sup>, as shown in **Figure S3d**. **Figure S3e** shows the relationship between  $\Delta T_{\max}$  and input power ( $P$ ), demonstrating good agreement between temperatures measured by SThM and simulated temperature at the breakdown power ( $P_{BD}$ ). The breakdown temperature ( $T_{BD}$ ) of ITO transistors on 30 nm HfO<sub>2</sub>/Si substrate is found to be  $\sim 272$ -340 °C. This  $T_{BD}$  was nearly double that of devices on 100 nm SiO<sub>2</sub>/Si substrates. Mechanical simulations of strain distribution along the ITO channel **Figure S3f** revealed compressive strain under the contacts and tensile strain in the channel region under initial conditions. Under breakdown conditions, the peak compressive strain was observed near the channel edges. Our results show that ITO

transistors on  $\text{HfO}_2$  substrates exhibit significantly higher breakdown power, enabled by enhanced heat dissipation and closer thermal expansion matching between ITO and  $\text{HfO}_2$ .

**Figure S3.** (a) Schematic of back-gated transistor, with 4 nm ITO channel on 30 nm  $\text{HfO}_2$ /Si ( $\text{p}^{++}$ ) substrate, and 80 nm Ni source and drain contacts. (b) Measured transfer curves of uncapped (black) and  $\text{Al}_2\text{O}_3$ -capped (light blue) devices, showing negative shift in threshold voltage, similar to our previous work.<sup>6</sup> (c) Measured  $I_D$  vs.  $V_{DS}$  curve of  $\text{Al}_2\text{O}_3$ -capped devices, showing linear behavior. (d) Sensitivity analysis of  $\Delta T_{\max}$  with respect to TBC at material interfaces, showing minimal dependence on TBC at ITO-Ni, ITO-Al<sub>2</sub>O<sub>3</sub>, and Ni-Al<sub>2</sub>O<sub>3</sub> interfaces. However,  $\Delta T_{\max}$  varies with the TBC of the ITO-HfO<sub>2</sub> interface, estimated as  $51 \pm 14 \text{ MWm}^{-2}\text{K}^{-1}$  by comparing to the SThM measurements. (e) Dependence of  $\Delta T_{\max}$  on input power,  $P$ . Filled symbols mark SThM-measured temperature, hollow symbol is a simulation of  $\Delta T_{\max}$  at  $P_{BD}$ . Dashed line is a linear fit, to highlight the trend. (f) Initial strain distribution ( $\epsilon_{xx}$ ) along the channel direction, showing tensile strain in the ITO channel and compressive strain under contacts (black curve). At device breakdown with self-heating, the compressive strain peaks at the channel/contact edge (red curve).

We note that the estimated TBCs for ITO-SiO<sub>2</sub> ( $\sim 35 \text{ MWm}^{-2}\text{K}^{-1}$ ) and ITO-HfO<sub>2</sub> ( $\sim 51 \text{ MWm}^{-2}\text{K}^{-1}$ ) are near the lower bound of typical TBCs for material interfaces,<sup>39</sup> but consistent with relatively low TBCs at the In<sub>2</sub>O<sub>3</sub>-HfO<sub>2</sub> interface<sup>40</sup> and those of other wide band gap material interfaces.<sup>41</sup> This can be due to phonon density of states mismatch between the materials and/or to material microstructure near the interface (as well as bonding strength), which could depend on deposition conditions. In addition, if the current flow in the ITO thickness is non-uniform, the effective TBC may appear lower by  $\sim 10\%$  (e.g. in the limit of current flowing entirely at the *top* ITO surface).

## S7. Breakdown Behavior of ALD-grown ITO Devices

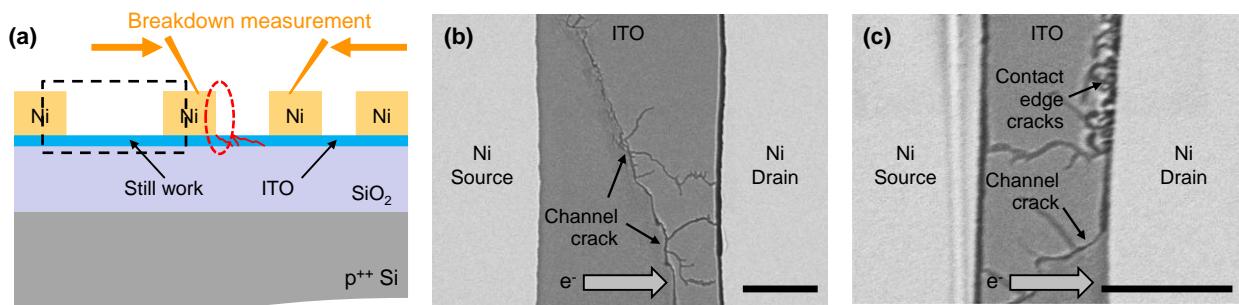

While this study mainly focused on the electro-thermal behavior of *sputtered* ITO devices, we also fabricated and characterized 3 nm thick ITO transistors grown by atomic layer deposition (ALD). **Figure S4a** illustrates the schematic of such back-gated devices on SiO<sub>2</sub>, patterned with varying channel lengths into transfer length method (TLM) structures. Electrical measurements up to breakdown did not affect neighboring devices, and the breakdown voltage and current of 1-2  $\mu\text{m}$  length channels were comparable to those of sputtered ITO transistors (**Figure 3** of main text).

Similar to the behavior of sputtered ITO transistors (main text), we also observe mechanical cracks from the drain side into the channel of ALD-grown ITO transistors (**Figure S4b-c**). While direct comparisons between sputtered and ALD-grown ITO transistors are limited due to differences in ITO thickness and electrical properties (e.g., threshold voltage), these findings suggest that similar high-field breakdown mechanisms occur in ALD-grown ITO transistors.

Given that ITO consists of 9:1  $\text{In}_2\text{O}_3:\text{SnO}_2$  by weight, it may be reasonable to expect that other In-dominated thin films transistors (e.g.  $\text{In}_2\text{O}_3$ , indium tungsten oxide, indium zinc oxide) have similar breakdown behaviors, although this topic warrants further research. On the other hand, thermal boundary conductance (TBC) is known to depend on factors such as material composition, interfacial bonding strength, and deposition conditions, making it difficult to predict TBC values for different amorphous oxide semiconductor interfaces with their gate insulators and contacts. Calculating TBC between amorphous materials from first principles also remains challenging (due to the lack of well-defined atomic structures and disordered interfacial bonding), thus we expect that experimental measurements will be needed for other (future) oxide semiconductor interfaces.

**Figure S4.** (a) Schematic of back-gated transistors with 3 nm *ALD-grown* ITO channel on 100 nm  $\text{SiO}_2/\text{Si}$  ( $\text{p}^{++}$ ) substrate, here patterned into TLM structures. (b) Scanning electron microscopy (SEM) image of a device after breakdown showing channel cracks, and (c) another device showing additional cracks near the Ni drain contact. Scale bars in (b-c) are all 1  $\mu\text{m}$ . Block arrows in (b, c) show the direction of electron flow. The observed breakdown mechanism is very similar to that of *sputtered* ITO devices with comparable channel lengths (**Figure 2** of the main text).

## SUPPORTING REFERENCES

- (1) Yalon, E.; McClellan, C. J.; Smithe, K. K. H.; Munoz Rojo, M.; Xu, R. L.; Suryavanshi, S. V.; Gabourie, A. J.; Neumann, C. M.; Xiong, F.; Farimani, A. B.; et al. Energy Dissipation in Monolayer  $\text{MoS}_2$  Electronics. *Nano Lett* **2017**, *17* (6), 3429-3433. DOI: 10.1021/acs.nanolett.7b00252.

- (2) Datye, I. M.; Rojo, M. M.; Yalon, E.; Deshmukh, S.; Mleczko, M. J.; Pop, E. Localized Heating and Switching in  $\text{MoTe}_2$ -Based Resistive Memory Devices. *Nano Lett* **2020**, *20* (2), 1461-1467. DOI: 10.1021/acs.nanolett.9b05272.

- (3) Deshmukh, S.; Rojo, M. M.; Yalon, E.; Vaziri, S.; Koroglu, C.; Islam, R.; Iglesias, R. A.; Saraswat, K.; Pop, E. Direct measurement of nanoscale filamentary hot spots in resistive memory devices. *Sci Adv* **2022**, *8* (13), eabk1514. DOI: 10.1126/sciadv.abk1514.

- (4) Swoboda, T.; Wainstein, N.; Deshmukh, S.; Koroglu, C.; Gao, X.; Lanza, M.; Hilgenkamp, H.; Pop, E.; Yalon, E.; Munoz Rojo, M. Nanoscale temperature sensing of electronic devices with

calibrated scanning thermal microscopy. *Nanoscale* **2023**, *15* (15), 7139-7146. DOI: 10.1039/d3nr00343d.

(5) Daus, A.; Vaziri, S.; Chen, V.; Körögöl, Ç.; Grady, R. W.; Bailey, C. S.; Lee, H. R.; Schauble, K.; Brenner, K.; Pop, E. High-performance flexible nanoscale transistors based on transition metal dichalcogenides. *Nat Electron* **2021**, *4* (7), 495-501. DOI: 10.1038/s41928-021-00598-6.

(6) Wahid, S.; Daus, A.; Kwon, J.; Qin, S.; Ko, J.-S.; Wong, H. S. P.; Pop, E. Effect of Top-Gate Dielectric Deposition on the Performance of Indium Tin Oxide Transistors. *IEEE Electron Device Letters* **2023**, *44* (6), 951-954. DOI: 10.1109/led.2023.3265316.

(7) Asheghi, M.; Kurabayashi, K.; Kasnavi, R.; Goodson, K. E. Thermal conduction in doped single-crystal silicon films. *J Appl Phys* **2002**, *91* (8), 5079-5088. DOI: 10.1063/1.1458057.

(8) Gabourie, A. J.; Polanco, C. A.; McClellan, C. J.; Su, H.; Malakoutian, M.; Körögöl, Ç.; Chowdhury, S.; Donadio, D.; Pop, E. AI-Accelerated Atoms-to-Circuits Thermal Simulation Pipeline for Integrated Circuit Design. In 2024 IEEE International Electron Devices Meeting (IEDM), 2024. DOI: 10.1109/iedm50854.2024.10873564.

(9) Lee, S. M.; Cahill, D. G. Heat transport in thin dielectric films. *J Appl Phys* **1997**, *81* (6), 2590-2595. DOI: 10.1063/1.363923.

(10) Zhu, W.; Zheng, G.; Cao, S.; He, H. Thermal conductivity of amorphous  $\text{SiO}_2$  thin film: A molecular dynamics study. *Sci Rep* **2018**, *8* (1), 10537. DOI: 10.1038/s41598-018-28925-6.

(11) Yoshikawa, T.; Yagi, T.; Oka, N.; Jia, J.; Yamashita, Y.; Hattori, K.; Seino, Y.; Taketoshi, N.; Baba, T.; Shigesato, Y. Thermal Conductivity of Amorphous Indium–Gallium–Zinc Oxide Thin Films. *Applied Physics Express* **2013**, *6* (2), 021101. DOI: 10.7567/apex.6.021101.

(12) Thuau, D.; Koymen, I.; Cheung, R. A microstructure for thermal conductivity measurement of conductive thin films. *Microelectronic Engineering* **2011**, *88* (8), 2408-2412. DOI: 10.1016/j.mee.2010.12.119.

(13) Brinzari, V. I.; Cocemasov, A. I.; Nika, D. L.; Korotcenkov, G. S. Ultra-low thermal conductivity of nanogranular indium tin oxide films deposited by spray pyrolysis. *Appl Phys Lett* **2017**, *110* (7), 071904. DOI: 10.1063/1.4976629.

(14) Cocemasov, A.; Brinzari, V.; Jeong, D. G.; Korotcenkov, G.; Vatavu, S.; Lee, J. S.; Nika, D. L. Thermal Transport Evolution Due to Nanostructural Transformations in Ga-Doped Indium-Tin-Oxide Thin Films. *Nanomaterials (Basel)* **2021**, *11* (5), 1126. DOI: 10.3390/nano11051126.

(15) Jia, J.; Yagi, T.; Shigesato, Y. Thermal conduction in polycrystalline or amorphous transparent conductive oxide films. *Solar Energy Materials and Solar Cells* **2024**, *271*, 112872. DOI: 10.1016/j.solmat.2024.112872.

(16) Zheng, X.; Cahill, D.; Krasnochtchekov, P.; Averback, R.; Zhao, J. High-throughput thermal conductivity measurements of nickel solid solutions and the applicability of the Wiedemann–Franz law. *Acta Materialia* **2007**, *55* (15), 5177-5185. DOI: 10.1016/j.actamat.2007.05.037.

(17) Cahill, D. G.; Braun, P. V.; Chen, G.; Clarke, D. R.; Fan, S.; Goodson, K. E.; Kebinski, P.; King, W. P.; Mahan, G. D.; Majumdar, A.; et al. Nanoscale thermal transport. II. 2003–2012. *Appl Phys Rev* **2014**, *1* (1), 011305. DOI: 10.1063/1.4832615.

(18) Cappella, A.; Battaglia, J. L.; Schick, V.; Kusiak, A.; Lamperti, A.; Wiemer, C.; Hay, B. High Temperature Thermal Conductivity of Amorphous  $\text{Al}_2\text{O}_3$  Thin Films Grown by Low Temperature ALD. *Advanced Engineering Materials* **2013**, *15* (11), 1046-1050. DOI: 10.1002/adem.201300132.

(19) Paterson, J.; Singhal, D.; Tainoff, D.; Richard, J.; Bourgeois, O. Thermal conductivity and thermal boundary resistance of amorphous  $\text{Al}_2\text{O}_3$  thin films on germanium and sapphire. *J Appl Phys* **2020**, *127* (24), 245105. DOI: 10.1063/5.0004576.

(20) Panzer, M. A.; Shandalov, M.; Rowlette, J. A.; Oshima, Y.; Yi Wei, C.; McIntyre, P. C.; Goodson, K. E. Thermal Properties of Ultrathin Hafnium Oxide Gate Dielectric Films. *IEEE Electron Device Letters* **2009**, *30* (12), 1269-1271. DOI: 10.1109/led.2009.2032937.

(21) Scott, E. A.; Gaskins, J. T.; King, S. W.; Hopkins, P. E. Thermal conductivity and thermal boundary resistance of atomic layer deposited high-k dielectric aluminum oxide, hafnium oxide, and titanium oxide thin films on silicon. *APL Materials* **2018**, *6* (5), 058302. DOI: 10.1063/1.5021044.

(22) Scott, E. A.; Smith, S. W.; Henry, M. D.; Rost, C. M.; Giri, A.; Gaskins, J. T.; Fields, S. S.; Jaszewski, S. T.; Ihlefeld, J. F.; Hopkins, P. E. Thermal resistance and heat capacity in hafnium zirconium oxide (HfZrO) dielectrics and ferroelectric thin films. *Appl Phys Lett* **2018**, *113* (19), 192901. DOI: 10.1063/1.5052244.

(23) Gabourie, A. J.; Körögülu, Ç.; Pop, E. Substrate-dependence of monolayer MoS<sub>2</sub> thermal conductivity and thermal boundary conductance. *J Appl Phys* **2022**, *131* (19), 195103. DOI: 10.1063/5.0089247.

(24) El-Kareh, B. *Fundamentals of Semiconductor Processing Technology*; 1995. DOI: 10.1007/978-1-4615-2209-6.

(25) Jaikissoon, M.; Körögülu, Ç.; Yang, J. A.; Neilson, K.; Saraswat, K. C.; Pop, E. CMOS-compatible strain engineering for monolayer semiconductor transistors. *Nat Electron* **2024**, *7* (10), 885-891. DOI: 10.1038/s41928-024-01244-7.