# Monte Carlo Simulation of Electrical Transport with Joule Heating and Strain in Monolayer MoS<sub>2</sub> Devices

Maritha A. Wang and Eric Pop\*

Cite This: *Nano Lett.* 2025, 25, 6841–6847

Read Online

ACCESS |

Metrics & More

Article Recommendations

Supporting Information

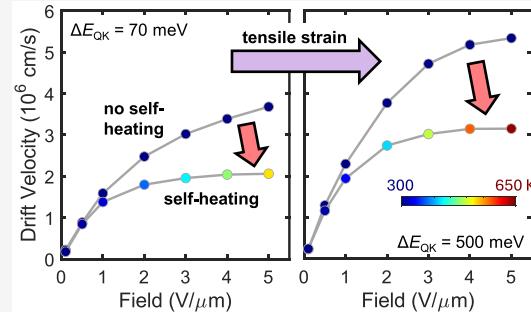

**ABSTRACT:** Two-dimensional (2D) semiconductors are candidates for future nanoscale (e.g., nanosheet) transistors, wherein high current densities and high-density integration cause self-heating, limiting performance and reliability. Here, we study the effects of self-heating and strain on electrical transport in monolayer MoS<sub>2</sub> using electro-thermal Monte Carlo simulations. Incorporating Joule self-heating with a generalizable thermal resistance model reveals that at high lateral field ( $\sim 5$  V/ $\mu$ m) and high charge carrier density ( $\sim 10^{13}$  cm $^{-2}$ ), transistor temperatures can increase by more than 200 K in steady state. The electron saturation velocity decreases to  $2.1 \times 10^6$  cm/s with self-heating but can reach  $5.3 \times 10^6$  cm/s at room temperature if self-heating is mitigated and tensile strain is applied to reduce intervalley scattering. Simulations also reveal that electron mean free paths are just 2–3 nm in this high-field regime. These results provide fundamental insights showing that both self-heating and strain must be considered in emerging 2D transistors.

**KEYWORDS:** MoS<sub>2</sub>, 2D transistor, self-heating, strain, mobility, high-field transport

Ultrathin transition metal dichalcogenides (TMDs), at the limit of a single layer, have attracted interest for nanoscale devices due to their atomic thinness, van der Waals interfaces, and mechanical strength. For example, such two-dimensional (2D) TMD semiconductors could be scaled beyond conventional silicon devices, which exhibit performance degradation at small dimensions due to increased surface scattering.<sup>1</sup> Recent studies have also suggested that such materials could play a role in three-dimensional (3D) heterogeneous integration of electronics, due to relatively lower synthesis temperatures.<sup>2–4</sup> Thus, it is becoming increasingly important to understand the fundamental limits of electrical transport in TMDs, especially in technology-relevant contexts, including substrates, strain, and temperature rise due to self-heating from device and circuit operation.

Despite relatively good thermal conductivity along the in-plane direction<sup>5</sup> (higher than silicon<sup>6</sup> in nanometer-thin films), common TMDs have relatively high thermal boundary resistance (TBR) at their out-of-plane interfaces<sup>5,7–9</sup> due to weaker van der Waals coupling with adjacent materials. Moreover, TMD transistors are likely to be surrounded by electrical insulators (e.g., SiO<sub>2</sub> or HfO<sub>2</sub>)<sup>10,11</sup> which also have low thermal conductivity. As a result, when current flows through an ultrathin TMD transistor channel, the Joule self-heating generated by electron–phonon interactions can lead to significant temperature rise,<sup>9</sup> resulting in performance degradation and reliability concerns. These effects could be exacerbated in technologies like nanosheet transistors,<sup>12–14</sup>

where channels are vertically stacked in very tight geometries with many interfaces and high current densities.

Here, we use the semi-classical Monte Carlo method<sup>15–21</sup> to investigate electrical transport in monolayer MoS<sub>2</sub> transistors with Joule self-heating and strain. This approach is well-suited for studying charge transport in semiconductors because it solves the Boltzmann Transport Equation directly and is fast compared to first-principles methods, while including quantum mechanical details like the energy band structure and electron–phonon scattering. Monte Carlo simulations of charge transport couple naturally with studies of thermal behavior because the energy exchanged in electron–phonon scattering events can be summed to yield the Joule heat dissipated. This approach has been previously used to examine self-heating<sup>22</sup> in Si, but not in TMD devices. Here, we simulate electron transport in monolayer MoS<sub>2</sub> including intrinsic (intravalley and intervalley) electron–phonon scattering, tensile strain, and heat loss to the substrate. We also evaluate device structures that allow us to compare our results with existing experimental measurements.<sup>9,23–25</sup> Our simulations are carried out with and without Joule self-heating and (varying

Received: October 21, 2024

Revised: March 28, 2025

Accepted: March 28, 2025

Published: April 16, 2025

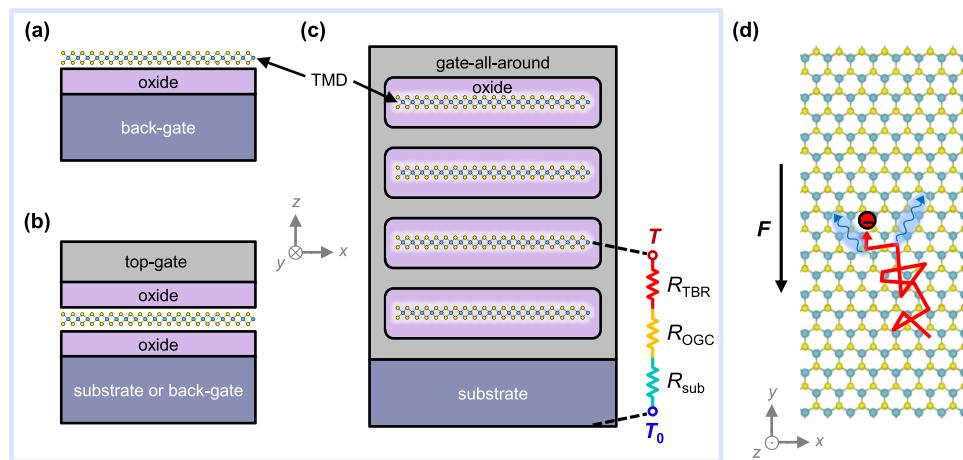

**Figure 1.** Cross-section schematics along the width of (a) a back-gated transistor,<sup>1,9</sup> (b) a dual-gated transistor,<sup>10</sup> and (c) a gate-all-around nanosheet transistor<sup>13</sup> with monolayer TMD channels, illustrating several use cases and the thermal resistance between the channel and substrate. This includes the thermal boundary resistance between TMD and gate oxide ( $R_{TBR}$ ), the combined thermal resistance of the oxide, gate stack, and contacts ( $R_{OGC}$ ), and the substrate thermal resistance ( $R_{sub}$ ). Current flow is in the  $y$ -direction, between source and drain contacts not shown in the cross-section. (d) Top-view schematic of the TMD channel with an electron drift trajectory (red) under the influence of an electric field  $F$  and phonon scattering (blue wavy arrows). Left/right boundaries are reflective ( $v_x$  becomes  $-v_x$ ), and top/bottom boundaries are periodic here.

levels of) strain, enabling us to place lower and upper bounds on the phonon-limited electron mobility and high-field saturation velocity. This work highlights the importance of incorporating Joule heating and strain in the analysis of emerging TMD transistor technologies.

The heat dissipation path in a transistor can be complex depending on the materials, interfaces, and geometry of the device.<sup>5,26–29</sup> For example, nanoscale dimensions reduce the thermal conductivity of materials,<sup>6,30</sup> while the thermal boundary resistance (TBR or Kapitza resistance) of interfaces<sup>5,8,9</sup> can also become a significant bottleneck. Figure 1a-c shows the cross-section schematics of three transistor geometries, from back-gated (most common for basic charge transport experiments)<sup>1,9</sup> to a future multi-channel nanosheet device.<sup>13</sup> A general thermal resistance model is also shown, which includes the thermal boundary resistance at the TMD-oxide interface ( $R_{TBR}$ ), the combined thermal resistance of the oxide, gate stack, and contacts ( $R_{OGC}$ ), and the thermal resistance of the substrate ( $R_{sub}$ ). Here,  $R_{OGC}$  incorporates most of the geometric complexity of the device and can be estimated from measurements<sup>9,29</sup> or from 3D device thermal simulations.  $R_{OGC}$  can include the various geometry-dependent device heat dissipation pathways, including contacts and gate stack, and their particular materials. This term can be updated for the specific device layout, allowing us to focus here on the fundamentals of self-heating in the TMD channel without loss of generality. To include Joule self-heating, we simulate electron–phonon scattering during device operation, then use a simplified thermal resistance model to capture the temperature rise, which is self-consistently used to update the scattering rates.

Our Monte Carlo simulation computes the trajectories and scattering of electrons in a monolayer MoS<sub>2</sub> channel, as shown in Figure 1d. This approach is advantageous vs first-principles or finite element methods because the time-dependent electron trajectories are explicitly simulated, incorporating fundamental physical details in the electron–phonon scattering rates, while remaining computationally inexpensive. The details of the general Monte Carlo approach are described elsewhere,<sup>15,31,32</sup> and some choices regarding our implementation

(e.g., vs earlier Si work) are given in **Supporting Information Section A**. Briefly, conduction band electrons are treated as charged particles, freely drifting in the  $x$ - $y$  plane of the 2D channel between scattering events. The energy band structure of the 2D semiconductor enters both the drift and scattering calculation, through the effective mass and density of states. The simulation takes place in constant time steps (1 fs), smaller than the shortest scattering time even at the highest temperatures considered. Electrons experience net drift due to the electric field, and at the end of each time step a scattering event (including self-scattering, where no electron–phonon scattering occurs) is selected by drawing a random number.<sup>15,31</sup> When electron–phonon scattering occurs, the energy exchanged with the TMD lattice is tallied (as heat) and the scattering angle is selected at random, isotropically.<sup>15,31</sup> This procedure repeats for the duration of the simulation, and the steady-state electron drift velocity is averaged for a given electric field. The low-field mobility is simply obtained as the ratio of this drift velocity and the magnitude of the field. Joule self-heating is captured by calculating the channel temperature rise from its power dissipation and thermal resistance ( $\Delta T = PR_{th}$ ), while iteratively updating the temperature-dependent scattering rates with the new temperature.<sup>32</sup>

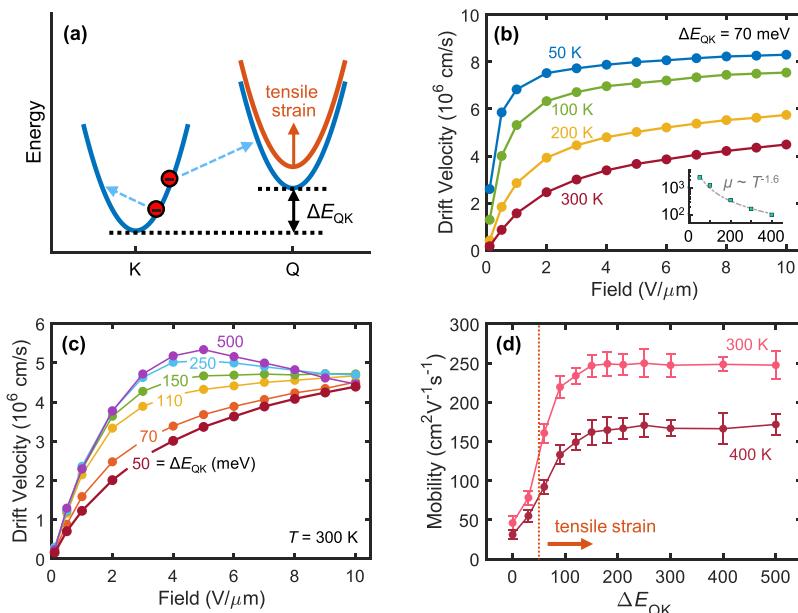

We first simulate charge transport along a MoS<sub>2</sub> channel considering intrinsic electron–phonon scattering without Joule heating. The TA, LA, TO(E'), LO(E'), and A<sub>1</sub> phonons are considered, which have the strongest electron–phonon coupling.<sup>16</sup> Figure 2a shows a schematic of the conduction band structure of monolayer MoS<sub>2</sub>. In unstrained MoS<sub>2</sub>, the K valley has a degeneracy of 2, and the Q valley has a degeneracy of 6 (the Q valley is sometimes called  $\Lambda$  or I,<sup>33,34</sup> approximately halfway along the  $\Gamma$ -K line<sup>35</sup>). Electrons experience both intravalley (K–K and Q–Q) and intervalley (K–Q) scattering, the latter more likely when the intervalley energy separation  $\Delta E_{QK}$  is relatively small. Here, we use electron–phonon scattering rates for intravalley and intervalley scattering with deformation potentials and phonon energies reported by Li et al.<sup>16</sup> for  $\Delta E_{QK} = 70$  meV (varying this as a function of strain, below). The Monte Carlo simulation parameters are summarized in **Supporting Information Section**

**Figure 2.** (a) Schematic of the monolayer MoS<sub>2</sub> conduction band. Tensile strain increases the energy separation  $\Delta E_{QK}$ . Dashed arrows mark electrons undergoing intravalley (K–K) and intervalley scattering (K–Q), here via phonon absorption. (b) Monte Carlo (MC) simulation of phonon-limited drift velocity vs electric field at various temperatures, as labeled. The inset shows the low-field electron mobility ( $\text{cm}^2\text{V}^{-1}\text{s}^{-1}$ ) vs temperature (K) with the dashed line indicating a fit of  $\mu \propto T^{-1.6}$ . The mobilities at 50 and 100 K (200 and 300 K) are extracted at a field of 0.1 V/μm (0.5 V/μm). (c) MC simulation of phonon-limited drift velocity vs electric field for different  $\Delta E_{QK}$  values, at 300 K. (d) Low-field electron mobilities vs  $\Delta E_{QK}$  at 300 and 400 K. Error bars represent standard deviations due to the statistical nature of MC simulations. The vertical dashed line marks a  $\Delta E_{QK}$  of 50 meV, the lowest bound predicted in the literature at 0% strain, and  $\Delta E_{QK}$  increases with tensile strain. The mobility saturates for  $\Delta E_{QK} > 150$  meV, but the high-field drift velocity benefits with an increased  $\Delta E_{QK}$ , as shown in panel (c).

B, and details of scattering rate calculations are discussed in **Supporting Information Section C**.

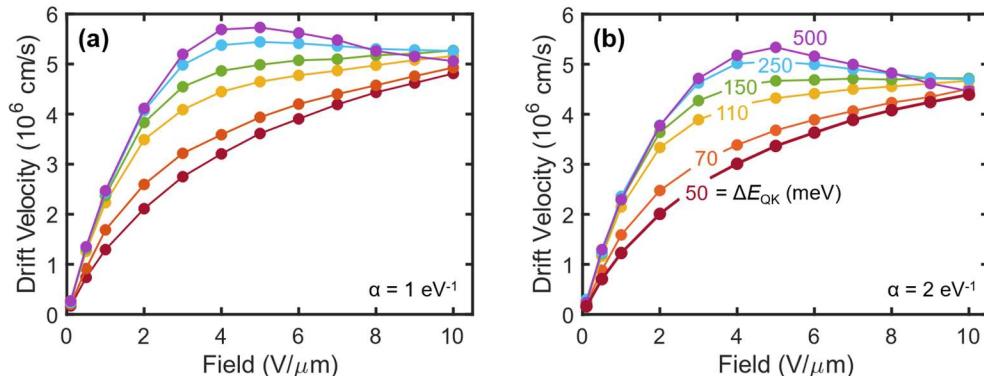

Effective masses at the K and Q valley minima are taken as  $m_c = 0.48m_0$  and  $0.57m_0$  respectively,<sup>36</sup> where  $m_0$  is the free electron rest mass. Additionally, because high-field transport reaches higher electron energies, we incorporate a non-parabolicity mass enhancement during electron drift, with  $m_{\text{eff}} = m_c(1 + 2\alpha E)$ , where  $\alpha = 2 \text{ eV}^{-1}$  for both K and Q valleys,<sup>20</sup> and  $E$  is the kinetic energy referenced to the bottom of the respective valley. (Other work<sup>37</sup> reported  $\alpha \approx 1 \text{ eV}^{-1}$ , but we have found using this value makes only a subtle difference in our high-field results, see **Supporting Information Section D**.) **Figure 2b** displays the simulated drift velocity vs electric field at various ambient temperatures, with  $\Delta E_{QK} = 70$  meV. The figure inset also shows that the low-field mobility decreases as  $\mu \propto T^{-1.6}$  when the temperature increases. (For a larger  $\Delta E_{QK} = 150$  meV, the low-field mobility decreases as  $\mu \propto T^{-1.4}$ .) The exponent of this temperature dependence is comparable to the theoretically predicted<sup>38,39</sup> value of  $-1.70$  and falls between experimental<sup>23,40,41</sup> values of  $-1.1$  and  $-1.9$ .

Tensile strain is known to increase the  $\Delta E_{QK}$  valley separation of monolayer TMDs, which was predicted to enhance electron mobility<sup>42,43</sup> by decreasing the intervalley (K–Q) scattering rate. Recent experiments have confirmed that tensile strain in monolayer MoS<sub>2</sub> can lead to between 1.6× to 2× mobility enhancement<sup>44,45</sup> (depending on strain type and magnitude), while biaxial tensile strain in monolayer WS<sub>2</sub> can lead to 2.3× mobility enhancement,<sup>46</sup> even in the presence of some disorder in experimental films. Note that  $\Delta E_{QK}$  in unstrained monolayer MoS<sub>2</sub> is presently not well-known, with theoretical calculations ranging from 50 to 270 meV,<sup>16–19,41–43,47,48</sup> and an experimental estimate of 110 meV.<sup>49</sup> To account for this range and the effect of tensile

strain, we simulate the drift velocity with  $\Delta E_{QK}$  between 50 to 500 meV in **Figure 2c**. (Here we raise all six Q valleys equally, which is more representative of biaxial strain, while uniaxial tensile strain may split the Q valleys<sup>42</sup> into degeneracies of 4 and 2, albeit with a relatively small energy difference.)

The drift velocities are sensitive to  $\Delta E_{QK}$ , i.e., a larger  $\Delta E_{QK}$  partially suppresses intervalley scattering, because fewer K valley electrons have sufficient energy to scatter into the Q valley. As a result, both the low-field mobility and high-field drift velocity increase when  $\Delta E_{QK}$  increases. When  $\Delta E_{QK} \leq 150$  meV in **Figure 2c**, the drift velocities appear to converge at the highest electric fields (>8 V/μm), because sufficient K valley electrons have energies in excess of the valley separation. However, for  $\Delta E_{QK} > 150$  meV we observe slight negative differential velocity (NDV) at the highest fields, as electrons access higher regions of the K valley with higher effective mass<sup>18</sup> due to band nonparabolicity. This is somewhat similar to the Gunn effect in GaAs and GaN,<sup>50</sup> however in these materials the NDV is primarily due to the much heavier effective mass of the upper valley.

The simulations carried out here are for electrons in uniform electric fields, at constant temperature and/or constant  $\Delta E_{QK}$  separation. In nanoscale transistors, the electric field can be very nonuniform,<sup>51</sup> and in strained transistors the strain can also be nonuniform.<sup>52–54</sup> Thus, our simulations cover the range of electric fields and strains likely to occur in practical devices. Nanoscale devices may also exhibit quasi-ballistic transport, with some electrons only scattering a few times before exiting the channel. (The phonon-limited electron mean free path for  $\Delta E_{QK} = 70$  meV ranges from ~5 nm at low-field to ~3 nm at high-field in our simulations, at room temperature. At lower mobilities, <80 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, the mean free path was previously estimated<sup>55</sup> to be <3 nm.) Thus, some electrons may

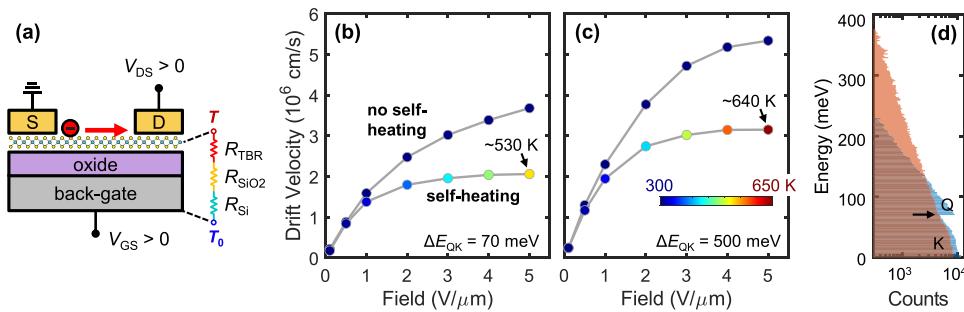

**Figure 3.** (a) Schematic of a back-gated monolayer MoS<sub>2</sub> transistor. The total thermal resistance includes the thermal boundary resistance of MoS<sub>2</sub> with the oxide ( $R_{TBR}$ ), the thermal resistance of the gate oxide ( $R_{SiO2}$ ), and the gate or substrate thermal resistance ( $R_{Si}$ ). This model can be generalized to other device geometries.<sup>5</sup> (b) Simulated electron drift velocity vs electric field along the channel, for a  $\Delta E_{QK}$  of 70 meV, with and without Joule self-heating. This represents the case with approximately no strain applied, and significant K–Q intervalley scattering. (c) Drift velocity vs field, for a  $\Delta E_{QK}$  of 500 meV, with and without Joule self-heating. This represents the case with significant tensile strain applied and K–Q intervalley scattering greatly suppressed. For panels (b) and (c), the initial temperature ( $T_0$ ) is 300 K and the electron density ( $n$ ) is  $10^{13}$  cm<sup>-2</sup>. These panels illustrate the upper and lower drift velocity limits, including both strain and self-heating effects. (d) Simulated electron distribution during high-field transport (5 V/ $\mu$ m), including self-heating, for  $\Delta E_{QK}$  values of 70 meV (blue) and 500 meV (orange). The zero energy is the K-valley minimum. The arrow marks the Q-valley minimum for the case with  $\Delta E_{QK}$  of 70 meV. Note the presence of high-energy (“hot”) electrons at hundreds of meV, which contribute to high-field transport, heating, and potential reliability concerns.<sup>59</sup>

overshoot the saturation velocity predicted here, as was observed in nanoscale Si transistors,<sup>56</sup> however, many electrons undergo sufficient scattering to render our results relevant even in quasi-ballistic<sup>57</sup> scenarios.

The low-field mobilities at 300 and 400 K for  $\Delta E_{QK}$  ranging from 0 to 500 meV are shown in Figure 2d. The mobility initially grows rapidly with  $\Delta E_{QK}$  but saturates for  $\Delta E_{QK} > 150$  meV. We note that the change of  $\Delta E_{QK}$  with percent strain is not well-known, but estimates range from 90 meV/% uniaxial strain to 150 meV/% biaxial strain for monolayer MoS<sub>2</sub>.<sup>17,41</sup> (For monolayer WS<sub>2</sub>, estimates range from 86 meV/% uniaxial strain to 169 meV/% biaxial strain.<sup>46</sup>) Over the full range of  $\Delta E_{QK}$  in Figure 2d, the room-temperature mobility can be enhanced by up to a factor of  $\sim 5\times$ , depending on the valley separation before tensile strain is applied. Here, our effective masses and electron–phonon deformation potentials are unscreened and independent of strain, but *ab initio* calculations which take these into account have predicted up to  $\sim 8\times$  mobility enhancement may be possible.<sup>41,58</sup>

We next include the effect of Joule self-heating on electron transport, which is relevant in most practical transistors,<sup>9</sup> e.g. when operating at current densities  $>100$   $\mu$ A/ $\mu$ m on common SiO<sub>2</sub>/Si substrates. To pick a concrete case related to existing experimental data,<sup>9,23</sup> we consider the simple thermal resistance of a back-gated transistor, as in Figure 3a. This thermal model can be generalized to include various heat flow paths (e.g., contacts<sup>5,23</sup>) and device geometries (e.g., gate-all-around or nanosheet transistors,<sup>27</sup> see Figure 1a-c). The thermal resistance of a long-channel back-gated transistor is  $R_{th} = R_{TBR} + R_{SiO2} + R_{Si}$ , where  $R_{TBR}$  is the MoS<sub>2</sub>/SiO<sub>2</sub> thermal boundary resistance,  $R_{SiO2}$  is the thermal resistance of SiO<sub>2</sub>, and  $R_{Si}$  is the thermal resistance of the Si substrate. With SiO<sub>2</sub> thickness of  $\sim 90$  nm and MoS<sub>2</sub>/SiO<sub>2</sub> thermal boundary conductance of  $\sim 15$  MWm<sup>-2</sup>K<sup>-1</sup>, the area-normalized thermal resistance of the MoS<sub>2</sub> channel at 300 K is  $R_{th} \approx 1.34 \times 10^{-7}$  m<sup>2</sup>KW<sup>-1</sup>. This is largely dominated by the (nearly equal)  $R_{TBR}$  and  $R_{SiO2}$  here, with the Si substrate thermal resistance having  $<5\%$  contribution for the typical micron-scale devices in previous experiments.<sup>9,23</sup> We note this simple model applies for device dimensions of microns or more (and much greater than the SiO<sub>2</sub> thickness), whereas nanoscale devices require

additional considerations, including heat loss to the contacts<sup>5</sup> (Supporting Information Section E).

For a power density  $P$ , normalized by the channel area, the steady-state temperature rise is  $\Delta T = PR_{th}$ . In our simulations, the power dissipated is obtained directly from electron–phonon scattering, as the net sum of phonon emission minus absorption energies,<sup>22</sup> per unit time. The power density can also be related to current flow through  $P = qnv_dF$ , where  $q$  is the elementary charge,  $n$  is the per-area electron density,  $v_d$  is the drift velocity, and  $F$  is the electric field magnitude. (This is equivalent to a total power  $I_D V_{DS}$  in a long-channel device, where  $I_D$  is the current.) We also iteratively update the temperature-dependent scattering rates with the calculated temperature ( $T = T_0 + \Delta T$ ) at each value of the electric field.

Figure 3b compares the simulated phonon-limited drift velocity for an electron density of  $n = 10^{13}$  cm<sup>-2</sup> with and without Joule heating, at  $\Delta E_{QK} = 70$  meV, which corresponds to very small or zero strain applied. Starting with an initial temperature  $T_0 = 300$  K, Joule heating causes a temperature rise  $\Delta T \approx 230$  K under high-field transport at 5 V/ $\mu$ m (power density  $\sim 1.7$  mW/ $\mu$ m<sup>2</sup>), with the device geometry considered here. This is equivalent to a temperature rise of  $\sim 135$  K at 1 mW/ $\mu$ m<sup>2</sup>, in good agreement with the experimental measurement<sup>9</sup> of  $\Delta T \approx 135$ –150 K in a long-channel monolayer MoS<sub>2</sub> transistor at this power density, with the same back-gate geometry as in our simulations. This self-heating effect, in steady-state, leads to decreased high-field electron drift velocity from  $3.7 \times 10^6$  cm/s to  $2.1 \times 10^6$  cm/s; correspondingly, the high-field electron mean free path drops to  $\sim 2$  nm.

Because electron transport at a given field depends on  $\Delta E_{QK}$  (Figure 2c), which is affected by strain, we also investigate the high-field drift velocity at high  $\Delta E_{QK} = 500$  meV, with and without Joule self-heating in Figure 3c. (This corresponds to high,  $\sim 3\%$  tensile strain assuming  $\Delta E_{QK}$  changes by  $\sim 150$  meV/% biaxial strain.<sup>17,41</sup>) At such high  $\Delta E_{QK}$  the intervalley scattering is strongly suppressed, and electron transport is dominated by K–K intravalley scattering. Starting with an initial temperature  $T_0 = 300$  K, Joule heating causes a temperature rise  $\Delta T \approx 340$  K at 5 V/ $\mu$ m lateral field, which is  $\sim 50\%$  greater than in Figure 3b at lower  $\Delta E_{QK} = 70$  meV. This occurs because the drift velocity is nearly 50% higher (3.1

$\times 10^6$  cm/s vs  $2.1 \times 10^6$  cm/s), while keeping  $n$  and  $F$  the same. If self-heating is entirely eliminated, the high-field drift velocity can reach up  $5.3 \times 10^6$  cm/s in this scenario (Figure 3c), with the assistance of suppressed intervalley scattering at high  $\Delta E_{QK}$ . Figure 3d shows the corresponding electron energy distribution at high field, with self-heating, for  $\Delta E_{QK} = 70$  meV and  $\Delta E_{QK} = 500$  meV. For the latter case, we observe that electrons reach higher energies when intervalley scattering is suppressed, which explains the higher  $v_{sat}$  seen in Figure 3c.

**Table 1. Comparison of the Monolayer MoS<sub>2</sub> Saturation Velocities from This Work and Experimental Studies<sup>a</sup>**

| Reference | Saturation velocity $v_{sat}$ (cm/s) |

|-----------|--------------------------------------|

| this work | $2.1-5.3 \times 10^6$                |

| 23        | $3.4 \times 10^6$                    |

| 24        | $5-7 \times 10^6$                    |

| 25        | $0.98 \times 10^6$                   |

| 63        | $3.8 \times 10^6$                    |

| 64        | $1.1 \times 10^6$                    |

<sup>a</sup>The lower (upper) range in our simulations includes (excludes) self-heating and considers low (high)  $\Delta E_{QK}$ . We note that experimental studies automatically include material defects and strain (from fabrication) as well as self-heating effects, unless the authors explicitly tried to reduce or account for self-heating.<sup>23,24</sup>

We also wish to compare the saturation velocities calculated in Figures 3b,c with the few experimental studies at high fields. Smithe et al.<sup>23</sup> estimated  $v_{sat} \approx 3.4 \times 10^6$  cm/s for electrons in monolayer MoS<sub>2</sub>, at room temperature, after accounting for self-heating with high-field measurements at lower ambient temperature. Nathawat et al.<sup>24</sup> obtained a higher  $v_{sat} \approx 5-7 \times 10^6$  cm/s with 4 ns voltage pulses, which limited both self-heating and electron trapping. The agreement with the range suggested by our Monte Carlo approach is good, but we recall that experimental MoS<sub>2</sub> samples tend to have defects and impurities, imperfectly controlled strain, as well as some uncertainty about their carrier density. These factors can lead to experimental estimates<sup>25</sup> (i.e.,  $v_{sat} \approx 0.98 \times 10^6$  cm/s) below our predicted range. Table 1 compares the present work with experimental estimates of the electron  $v_{sat}$  in this material.

While self-heating is known to limit current flow for 2D transistors in direct-current (DC) operation,<sup>9,60</sup> devices working at GHz frequencies and/or in digital switching with low duty cycle will heat up less when their on-state time is shorter than their thermal time constant. For reference, the thermal time constant of 2D material devices ranges between 30 to 300 ns, depending on the thickness and type of layers surrounding the channel,<sup>61</sup> because the 2D monolayer contributes negligible thermal capacitance. Ultrathin silicon-on-insulator (SOI) devices were also found to experience less self-heating in high frequency operation than in DC operation due to thermal time constants around 100 ns.<sup>62</sup>

In summary, we used Monte Carlo simulations to study the effects of Joule self-heating and strain in monolayer MoS<sub>2</sub> transistors, particularly during high-field operation. Tensile strain increases the K-Q valley energy separation and enhances the electron mobility by up to  $\sim 5\times$ , but this effect saturates for  $\Delta E_{QK} > 150$  meV. In contrast, larger tensile strains continue to increase the saturation velocity, until K-Q intervalley scattering is entirely suppressed. In this limit, the electron  $v_{sat}$  can reach  $>5.0 \times 10^6$  cm/s, at 300 K, corresponding to a current density  $>1.3$  mA/ $\mu$ m at electron

densities which can be achieved in practice.<sup>10,60</sup> When self-heating is included in DC operation, the device temperature can rise by over 230 K, and the high-field drift velocity is reduced by over 40%. Because our simulations include only intrinsic phonon scattering, the higher predicted drift velocities (with no self-heating and extreme strain) represent upper bounds. In contrast, the lower values (with extreme self-heating and  $\sim 0\%$  strain) are likely lower bounds, because self-heating is overestimated in DC operation and because practical, nanoscale devices are expected to include strain,<sup>53</sup> and to benefit from heat loss to contacts.<sup>5</sup>

This approach can also be extended to analyze other 2D semiconductors or hole transport. Finally, while our simulations are in a long-channel regime of uniform high-field, self-heating is expected to play a role even in very short,  $\sim 10$  nm scale quasi-ballistic transistors<sup>57</sup> because the electron mean free path is estimated to be  $\sim 3$  nm during high-field transport ( $\sim 2$  nm with self-heating). Future studies could incorporate factors relevant for nanoscale gate-all-around transistors including both the electrical and thermal effects of contacts, charged impurity scattering, as well as scattering by ‘remote phonons’ (interface plasmon-phonon scattering),<sup>65</sup> with practical gate insulators like HfO<sub>2</sub>.<sup>10</sup> The latter may introduce a trade-off between additional scattering and lower direct self-heating, with some heat being generated not in the MoS<sub>2</sub> channel but in the surrounding dielectric (i.e., indirect heating).

## ■ ASSOCIATED CONTENT

### SI Supporting Information

The Supporting Information is available free of charge at <https://pubs.acs.org/doi/10.1021/acs.nanolett.4c05254>.

Additional simulation details (including simulation parameters and scattering rate calculation), band nonparabolicity analysis, and discussion of device lateral heat dissipation ([PDF](#))

## ■ AUTHOR INFORMATION

### Corresponding Author

Eric Pop – Department of Electrical Engineering and Department of Applied Physics, Stanford University, Stanford, California 94305, United States; Department of Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0000-0003-0436-8534](https://orcid.org/0000-0003-0436-8534); Email: [epop@stanford.edu](mailto:epop@stanford.edu)

### Author

Maritha A. Wang – Department of Materials Science and Engineering, Stanford University, Stanford, California 94305, United States; [orcid.org/0009-0002-6160-5030](https://orcid.org/0009-0002-6160-5030)

Complete contact information is available at:

<https://pubs.acs.org/doi/10.1021/acs.nanolett.4c05254>

### Notes

The authors declare no competing financial interest.

## ■ ACKNOWLEDGMENTS

M.A.W. acknowledges support from the National Science Foundation (NSF) Graduate Research Fellowship and the Shoucheng Zhang Fellowship, a Stanford Graduate Fellowship. This work was also supported in part by SUPREME, a JUMP 2.0 Center sponsored by the Semiconductor Research Corp.

(SRC) and DARPA, by Intel Corp., and by the Stanford SystemX Alliance.

## ■ REFERENCES

- (1) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to  $\text{MoS}_2$  Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* **2016**, *16* (6), 3824–3830.

- (2) Tang, A.; Kumar, A.; Jaikissoon, M.; Saraswat, K.; Wong, H.-S. P.; Pop, E. Toward Low-Temperature Solid-Source Synthesis of Monolayer  $\text{MoS}_2$ . *ACS Appl. Mater. Interfaces* **2021**, *13* (35), 41866–41874.

- (3) Zhu, J.; Park, J.-H.; Vitale, S. A.; Ge, W.; Jung, G. S.; Wang, J.; Mohamed, M.; Zhang, T.; Ashok, M.; Xue, M.; Zheng, X.; Wang, Z.; Hansryd, J.; Chandrasekaran, A. P.; Kong, J.; Palacios, T. Low-Thermal-Budget Synthesis of Monolayer Molybdenum Disulfide for Silicon Back-End-of-Line Integration on a 200 Mm Platform. *Nat. Nanotechnol.* **2023**, *18* (5), 456–463.

- (4) Hoang, A. T.; Hu, L.; Kim, B. J.; Van, T. T. N.; Park, K. D.; Jeong, Y.; Lee, K.; Ji, S.; Hong, J.; Katiyar, A. K.; Shong, B.; Kim, K.; Im, S.; Chung, W. J.; Ahn, J.-H. Low-Temperature Growth of  $\text{MoS}_2$  on Polymer and Thin Glass Substrates for Flexible Electronics. *Nat. Nanotechnol.* **2023**, *18* (12), 1439–1447.

- (5) Gabourie, A. J.; Körögöl, Ç.; Pop, E. Substrate-Dependence of Monolayer  $\text{MoS}_2$  Thermal Conductivity and Thermal Boundary Conductance. *J. Appl. Phys.* **2022**, *131* (19), 195103.

- (6) Neogi, S.; Reparaz, J. S.; Pereira, L. F. C.; Graczykowski, B.; Wagner, M. R.; Sledzinska, M.; Shchepetov, A.; Prunnila, M.; Ahopelto, J.; Sotomayor-Torres, C. M.; Donadio, D. Tuning Thermal Transport in Ultrathin Silicon Membranes by Surface Nanoscale Engineering. *ACS Nano* **2015**, *9* (4), 3820–3828.

- (7) Yalon, E.; Aslan, B.; Smithe, K. K. H.; McClellan, C. J.; Suryavanshi, S. V.; Xiong, F.; Sood, A.; Neumann, C. M.; Xu, X.; Goodson, K. E.; Heinz, T. F.; Pop, E. Temperature-Dependent Thermal Boundary Conductance of Monolayer  $\text{MoS}_2$  by Raman Thermometry. *ACS Appl. Mater. Interfaces* **2017**, *9* (49), 43013–43020.

- (8) Pop, E. Energy Dissipation and Transport in Nanoscale Devices. *Nano Res.* **2010**, *3* (3), 147–169.

- (9) Yalon, E.; McClellan, C. J.; Smithe, K. K. H.; Muñoz Rojo, M.; Xu, R. L.; Suryavanshi, S. V.; Gabourie, A. J.; Neumann, C. M.; Xiong, F.; Farimani, A. B.; Pop, E. Energy Dissipation in Monolayer  $\text{MoS}_2$  Electronics. *Nano Lett.* **2017**, *17* (6), 3429–3433.

- (10) Ko, J.-S.; Shearer, A.; Lee, S.; Neilson, K.; Jaikissoon, M.; Kim, K.; Bent, S.; Pop, E.; Saraswat, K. Achieving 1-nm-Scale Equivalent Oxide Thickness Top Gate Dielectric on Monolayer Transition Metal Dichalcogenide Transistors with CMOS-Friendly Approaches. *IEEE Trans. Electron Devices* **2025**, *72*, 1514–1519.

- (11) Illarionov, Y. Y.; Knobloch, T.; Jech, M.; Lanza, M.; Akinwande, D.; Vexler, M. I.; Mueller, T.; Lemme, M. C.; Fiori, G.; Schwierz, F.; Grasser, T. Insulators for 2D Nanoelectronics: The Gap to Bridge. *Nat. Commun.* **2020**, *11* (1), 3385.

- (12) O'Brien, K. P.; Dorow, C. J.; Penumatcha, A.; Maxey, K.; Lee, S.; Naylor, C. H.; Hsiao, A.; Holybee, B.; Rogan, C.; Adams, D.; Tronic, T.; Ma, S.; Oni, A.; Gupta, A. S.; Bristol, R.; Clendenning, S.; Metz, M.; Avci, U. Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering. *2021 IEEE International Electron Devices Meeting (IEDM)* **2021**, 7.1.1–7.1.4.

- (13) Dorow, C.; O'Brien, K.; Naylor, C. H.; Lee, S.; Penumatcha, A.; Hsiao, A.; Tronic, T.; Christenson, M.; Maxey, K.; Zhu, H.; Oni, A.; Alaan, U.; Gosavi, T.; Gupta, A. S.; Bristol, R.; Clendenning, S.; Metz, M.; Avci, U. Advancing Monolayer 2-D nMOS and pMOS Transistor Integration From Growth to Van Der Waals Interface Engineering for Ultimate CMOS Scaling. *IEEE Trans. Electron Devices* **2021**, *68* (12), 6592–6598.

- (14) Chung, Y.-Y.; Chou, B.-J.; Hsu, C.-F.; Yun, W.-S.; Li, M.-Y.; Su, S.-K.; Liao, Y.-T.; Lee, M.-C.; Huang, G.-W.; Liew, S.-L.; Shen, Y.-Y.; Chang, W.-H.; Chen, C.-W.; Kei, C.-C.; Wang, H.; Philip Wong, H.-S.; Lee, T. Y.; Chien, C.-H.; Cheng, C.-C.; Radu, I. P. First Demonstration of GAA Monolayer- $\text{MoS}_2$  Nanosheet nFET with 410  $\mu\text{A}/\mu\text{m} \text{I}_D$  at 1V  $V_D$  at 40nm Gate Length. *2022 International Electron Devices Meeting (IEDM)* **2022**, 34.5.1–34.5.4.

- (15) Jacoboni, C.; Reggiani, L. The Monte Carlo Method for the Solution of Charge Transport in Semiconductors with Applications to Covalent Materials. *Rev. Mod. Phys.* **1983**, *55* (3), 645–705.

- (16) Li, X.; Mullen, J. T.; Jin, Z.; Borysenko, K. M.; Buongiorno Nardelli, M.; Kim, K. W. Intrinsic Electrical Transport Properties of Monolayer Silicene and  $\text{MoS}_2$  from First Principles. *Phys. Rev. B* **2013**, *87* (11), 115418.

- (17) Bhatti, A. A.; Archer, B. T.; Navlakha, N.; Register, L. F.; Banerjee, S. K. Semi-Classical Monte Carlo Study of the Impact of Tensile Strain on the Performance Limits of Monolayer  $\text{MoS}_2$  n-Channel MOSFETs. *J. Appl. Phys.* **2023**, *134* (20), 204302.

- (18) Zhang, C.; Cheng, L.; Liu, Y. Understanding High-Field Electron Transport Properties and Strain Effects of Monolayer Transition Metal Dichalcogenides. *Phys. Rev. B* **2020**, *102* (11), 115405.

- (19) Jin, Z.; Li, X.; Mullen, J. T.; Kim, K. W. Intrinsic Transport Properties of Electrons and Holes in Monolayer Transition-Metal Dichalcogenides. *Phys. Rev. B* **2014**, *90* (4), 045422.

- (20) Ferry, D. K. Electron Transport in Some Transition Metal Dichalcogenides:  $\text{MoS}_2$  and  $\text{WS}_2$ . *Semicond. Sci. Technol.* **2017**, *32* (8), 085003.

- (21) Pilotto, A.; Khakbaz, P.; Palestri, P.; Esseni, D. Semi-Classical Transport in  $\text{MoS}_2$  and  $\text{MoS}_2$  Transistors by a Monte Carlo Approach. *Solid-State Electron.* **2022**, *192*, 108295.

- (22) Pop, E.; Dutton, R. W.; Goodson, K. E. Monte Carlo Simulation of Joule Heating in Bulk and Strained Silicon. *Appl. Phys. Lett.* **2005**, *86* (8), 082101.

- (23) Smithe, K. K. H.; English, C. D.; Suryavanshi, S. V.; Pop, E. High-Field Transport and Velocity Saturation in Synthetic Monolayer  $\text{MoS}_2$ . *Nano Lett.* **2018**, *18* (7), 4516–4522.

- (24) Nathawat, J.; Smithe, K. K. H.; English, C. D.; Yin, S.; Dixit, R.; Randle, M.; Arabchigavkani, N.; Barut, B.; He, K.; Pop, E.; Bird, J. P. Transient Hot-Carrier Dynamics and Intrinsic Velocity Saturation in Monolayer  $\text{MoS}_2$ . *Phys. Rev. Mater.* **2020**, *4* (1), 014002.

- (25) Liu, W.; Sarkar, D.; Kang, J.; Cao, W.; Banerjee, K. Impact of Contact on the Operation and Performance of Back-Gated Monolayer  $\text{MoS}_2$  Field-Effect-Transistors. *ACS Nano* **2015**, *9* (8), 7904–7912.

- (26) Takahashi, T.; Beppu, N.; Chen, K.; Oda, S.; Uchida, K. Self-Heating Effects and Analog Performance Optimization of Fin-Type Field-Effect Transistors. *Jpn. J. Appl. Phys.* **2013**, *52* (4S), 04CC03.

- (27) Song, Y. S.; Kim, H.; Hyun Kim, J. Improvement of Thermal Characteristics and On-Current in Vertically Stacked Nanosheet FET by Parasitic Channel Height Engineering. *IEEE Access* **2024**, *12*, 105878–105886.

- (28) Jang, D.; Bury, E.; Ritzenthaler, R.; Bardon, M. G.; Chiarella, T.; Miyaguchi, K.; Raghavan, P.; Mocuta, A.; Groeseneken, G.; Mercha, A.; Verkest, D.; Thean, A. Self-Heating on Bulk FinFET from 14nm down to 7nm Node. *2015 IEEE International Electron Devices Meeting (IEDM)* **2015**, 11.6.1–11.6.4.

- (29) Takahashi, T.; Matsuki, T.; Shinada, T.; Inoue, Y.; Uchida, K. Direct Evaluation of Self-Heating Effects in Bulk and Ultra-Thin BOX SOI MOSFETs Using Four-Terminal Gate Resistance Technique. *IEEE J. Electron Devices Soc.* **2016**, *4* (5), 365–373.

- (30) Bae, M.-H.; Li, Z.; Aksamija, Z.; Martin, P. N.; Xiong, F.; Ong, Z.-Y.; Knezevic, I.; Pop, E. Ballistic to Diffusive Crossover of Heat Flow in Graphene Ribbons. *Nat. Commun.* **2013**, *4* (1), 1734.

- (31) Lundstrom, M. *Fundamentals of Carrier Transport*, 2nd ed.; Cambridge University Press: Cambridge, U.K., 2000.

- (32) Pop, E.; Dutton, R. W.; Goodson, K. E. Analytic Band Monte Carlo Model for Electron Transport in Si Including Acoustic and Optical Phonon Dispersion. *J. Appl. Phys.* **2004**, *96* (9), 4998–5005.

- (33) Pimenta, M. A.; del Corro, E.; Carvalho, B. R.; Fantini, C.; Malard, L. M. Comparative Study of Raman Spectroscopy in Graphene and  $\text{MoS}_2$ -Type Transition Metal Dichalcogenides. *Acc. Chem. Res.* **2015**, *48* (1), 41–47.

(34) Barré, E.; Dandu, M.; Kundu, S.; Sood, A.; da Jornada, F. H.; Raja, A. Engineering Interlayer Hybridization in van Der Waals Bilayers. *Nat. Rev. Mater.* **2024**, *9* (7), 499–508.

(35) Rasmussen, F. A.; Thygesen, K. S. Computational 2D Materials Database: Electronic Structure of Transition-Metal Dichalcogenides and Oxides. *J. Phys. Chem. C* **2015**, *119* (23), 13169–13183.

(36) Li, S.-L.; Tsukagoshi, K.; Orgiu, E.; Samori, P. Charge Transport and Mobility Engineering in Two-Dimensional Transition Metal Chalcogenide Semiconductors. *Chem. Soc. Rev.* **2016**, *45* (1), 118–151.

(37) Hosseini, M.; Elahi, M.; Pourfath, M.; Esseni, D. Very Large Strain Gauges Based on Single Layer MoSe<sub>2</sub> and WSe<sub>2</sub> for Sensing Applications. *Appl. Phys. Lett.* **2015**, *107* (25), 253503.

(38) Kaasbjerg, K.; Thygesen, K. S.; Jacobsen, K. W. Phonon-Limited Mobility in n-Type Single-Layer MoS<sub>2</sub> from First Principles. *Phys. Rev. B* **2012**, *85* (11), 115317.

(39) Yu, Z.; Ong, Z.-Y.; Li, S.; Xu, J.-B.; Zhang, G.; Zhang, Y.-W.; Shi, Y.; Wang, X. Analyzing the Carrier Mobility in Transition-Metal Dichalcogenide MoS<sub>2</sub> Field-Effect Transistors. *Adv. Funct. Mater.* **2017**, *27* (19), 1604093.

(40) Cui, X.; Lee, G.-H.; Kim, Y. D.; Arefe, G.; Huang, P. Y.; Lee, C.-H.; Chenet, D. A.; Zhang, X.; Wang, L.; Ye, F.; Pizzocchero, F.; Jessen, B. S.; Watanabe, K.; Taniguchi, T.; Muller, D. A.; Low, T.; Kim, P.; Hone, J. Multi-Terminal Transport Measurements of MoS<sub>2</sub> Using a van Der Waals Heterostructure Device Platform. *Nat. Nanotechnol.* **2015**, *10* (6), 534–540.

(41) Liu, X.; Erbas, B.; Conde-Rubio, A.; Rivano, N.; Wang, Z.; Jiang, J.; Bienz, S.; Kumar, N.; Sohier, T.; Penedo, M.; Banerjee, M.; Fantner, G.; Zenobi, R.; Marzari, N.; Kis, A.; Boero, G.; Brugger, J. Deterministic Grayscale Nanotopography to Engineer Mobilities in Strained MoS<sub>2</sub> FETs. *Nat. Commun.* **2024**, *15* (1), 6934.

(42) Hosseini, M.; Elahi, M.; Pourfath, M.; Esseni, D. Strain Induced Mobility Modulation in Single-Layer MoS<sub>2</sub>. *J. Phys. Appl. Phys.* **2015**, *48* (37), 375104.

(43) Hosseini, M.; Elahi, M.; Pourfath, M.; Esseni, D. Strain-Induced Modulation of Electron Mobility in Single-Layer Transition Metal Dichalcogenides MX<sub>2</sub> (M = Mo, W; X = S, Se). *IEEE Trans. Electron Devices* **2015**, *62* (10), 3192–3198.

(44) Datye, I. M.; Daus, A.; Grady, R. W.; Brenner, K.; Vaziri, S.; Pop, E. Strain-Enhanced Mobility of Monolayer MoS<sub>2</sub>. *Nano Lett.* **2022**, *22* (20), 8052–8059.

(45) Zhang, Y.; Zhao, H. L.; Huang, S.; Hossain, M. A.; van der Zande, A. M. Enhancing Carrier Mobility in Monolayer MoS<sub>2</sub> Transistors with Process-Induced Strain. *ACS Nano* **2024**, *18* (19), 12377–12385.

(46) Yang, J. A.; Bennett, R. K. A.; Hoang, L.; Zhang, Z.; Thompson, K. J.; Michail, A.; Parthenios, J.; Papagelis, K.; Mannix, A. J.; Pop, E. Biaxial Tensile Strain Enhances Electron Mobility of Monolayer Transition Metal Dichalcogenides. *ACS Nano* **2024**, *18* (28), 18151–18159.

(47) Gaddeman, G.; Gopalan, S.; Van De Put, M. L.; Fischetti, M. V. Limitations of Ab Initio Methods to Predict the Electronic-Transport Properties of Two-Dimensional Semiconductors: The Computational Example of 2H-Phase Transition Metal Dichalcogenides. *J. Comput. Electron.* **2021**, *20* (1), 49–59.

(48) Kadantsev, E. S.; Hawrylak, P. Electronic Structure of a Single MoS<sub>2</sub> Monolayer. *Solid State Commun.* **2012**, *152* (10), 909–913.

(49) Hill, H. M.; Rigosi, A. F.; Rim, K. T.; Flynn, G. W.; Heinz, T. F. Band Alignment in MoS<sub>2</sub>/WS<sub>2</sub> Transition Metal Dichalcogenide Heterostructures Probed by Scanning Tunneling Microscopy and Spectroscopy. *Nano Lett.* **2016**, *16* (8), 4831–4837.

(50) Ferry, D. K. *Hot Carriers in Semiconductors*; IOP Publishing, 2021.

(51) Chaudhry, A.; Kumar, M. J. Controlling Short-Channel Effects in Deep-Submicron SOI MOSFETs for Improved Reliability: A Review. *IEEE Trans. Device Mater. Reliab.* **2004**, *4* (1), 99–109.

(52) Jaikissoon, M.; Pop, E.; Saraswat, K. C. Strain Induced by Evaporated-Metal Contacts on Monolayer MoS<sub>2</sub> Transistors. *IEEE Electron Device Lett.* **2024**, *45* (8), 1528–1531.

(53) Jaikissoon, M.; Körögöl, Ç.; Yang, J. A.; Neilson, K.; Saraswat, K. C.; Pop, E. CMOS-Compatible Strain Engineering for Monolayer Semiconductor Transistors. *Nat. Electron.* **2024**, *7* (10), 885–891.

(54) Hoang, L.; Jaikissoon, M.; Körögöl, Ç.; Zhang, Z.; Bennett, R. K. A.; Song, J.-H.; Yang, J. A.; Ko, J.-S.; Brongersma, M. L.; Saraswat, K. C.; Pop, E.; Mannix, A. J. Understanding the Impact of Contact-Induced Strain on the Electrical Performance of Monolayer WS<sub>2</sub> Transistors. *Nano Lett.* **2024**, *24* (41), 12768–12774.

(55) Smithe, K. K. H.; English, C. D.; Suryavanshi, S. V.; Pop, E. Intrinsic Electrical Transport and Performance Projections of Synthetic Monolayer MoS<sub>2</sub> Devices. *2D Mater.* **2017**, *4* (1), 011009.

(56) Assaderaghi, F.; Sinitsky, D.; Bokor, J.; Ko, P. K.; Gaw, H.; Hu, C. High-Field Transport of Inversion-Layer Electrons and Holes Including Velocity Overshoot. *IEEE Trans. Electron Devices* **1997**, *44* (4), 664–671.

(57) Stieger, C.; Szabo, A.; Bunjaku, T.; Luisier, M. *Ab-Initio* Quantum Transport Simulation of Self-Heating in Single-Layer 2-D Materials. *J. Appl. Phys.* **2017**, *122* (4), 045708.

(58) Sohier, T.; De Melo, P. M. M. C.; Zanolli, Z.; Verstraete, M. J. The Impact of Valley Profile on the Mobility and Kerr Rotation of Transition Metal Dichalcogenides. *2D Mater.* **2023**, *10* (2), 025006.

(59) Lan, H.-Y.; Yang, S.-H.; Kantre, K.-A.; Cott, D.; Tripathi, R.; Appenzeller, J.; Chen, Z. Reliability of High-Performance Monolayer MoS<sub>2</sub> Transistors on Scaled High- $\kappa$  HfO<sub>2</sub>. *Npj 2D Mater. Appl.* **2025**, *9* (1), 5.

(60) McClellan, C. J.; Yalon, E.; Smithe, K. K. H.; Suryavanshi, S. V.; Pop, E. High Current Density in Monolayer MoS<sub>2</sub> Doped by AlO<sub>x</sub>. *ACS Nano* **2021**, *15* (1), 1587–1596.

(61) Islam, S.; Li, Z.; Dorgan, V. E.; Bae, M.-H.; Pop, E. Role of Joule Heating on Current Saturation and Transient Behavior of Graphene Transistors. *IEEE Electron Device Lett.* **2013**, *34* (2), 166–168.

(62) Polonsky, S.; Jenkins, K. A. Time-Resolved Measurements of Self-Heating in SOI and Strained-Silicon MOSFETs Using Photon Emission Microscopy. *IEEE Electron Device Lett.* **2004**, *25* (4), 208–210.

(63) He, G.; Ghosh, K.; Singisetti, U.; Ramamoorthy, H.; Somphonsane, R.; Bohra, G.; Matsunaga, M.; Higuchi, A.; Aoki, N.; Najmaei, S.; Gong, Y.; Zhang, X.; Vajtai, R.; Ajayan, P. M.; Bird, J. P. Conduction Mechanisms in CVD-Grown Monolayer MoS<sub>2</sub> Transistors: From Variable-Range Hopping to Velocity Saturation. *Nano Lett.* **2015**, *15* (8), 5052–5058.

(64) Sebastian, A.; Pendurthi, R.; Choudhury, T. H.; Redwing, J. M.; Das, S. Benchmarking Monolayer MoS<sub>2</sub> and WS<sub>2</sub> Field-Effect Transistors. *Nat. Commun.* **2021**, *12* (1), 693.

(65) Gopalan, S.; Mansoori, S.; Van De Put, M.; Gaddeman, G.; Fischetti, M. Monte Carlo Study of Carrier Transport in Two-Dimensional Transition Metal Dichalcogenides: High-Field Characteristics and MOSFET Simulation. *J. Comput. Electron.* **2023**, *22* (5), 1240–1256.

## ■ NOTE ADDED AFTER ASAP PUBLICATION

Additional corrections were made to this paper after it was published ASAP on April 16, 2025. The corrected version reposted on April 21, 2025.

## Supporting Information

### **Monte Carlo Simulation of Electrical Transport with Joule Heating and Strain in Monolayer MoS<sub>2</sub> Devices**

Maritha A. Wang<sup>1</sup> and Eric Pop<sup>1,2,3,\*</sup>

<sup>1</sup> Department of Materials Science and Engineering, Stanford University, Stanford, CA 94305, USA.

<sup>2</sup> Department of Electrical Engineering, Stanford University, Stanford, CA 94305, USA.

<sup>3</sup> Department of Applied Physics, Stanford University, Stanford, CA 94305, USA.

\*Contact: [epop@stanford.edu](mailto:epop@stanford.edu)

#### **Section A. Monolayer MoS<sub>2</sub> Monte Carlo Simulation vs. Si-based Monte Carlo Simulation**

The simulation code used in this study was developed from the ground up, inspired by earlier work which studied Joule heating in Si using Monte Carlo simulations<sup>1</sup> (Ref. [22] in our main manuscript text). The Si simulations included analytic expressions of the electron band structure (with and without strain) and phonon dispersion, while the electron-phonon scattering rates were numerically calculated in the deformation potential formalism, accounting for intravalley and intervalley scattering.<sup>2,3</sup> Multiple electrons were concurrently simulated (in the Ensemble Monte Carlo Method, EMC), for which statistics can be collected (e.g. the drift velocity  $v_d$ ) when the simulation is run for a sufficiently long time. The EMC can also be employed to calculate the spatial distribution of heat generated in a device.<sup>4,5</sup> Joule heating of the Si lattice was accounted for by tallying the energy exchange between electrons and the lattice during the electron-phonon scattering processes, and the final energy (heat) dissipation rates were reported.

In the present work, to simulate electron transport with strain and self-heating in two-dimensional (2D) devices, we calculated the electron-phonon scattering rates for monolayer MoS<sub>2</sub> using the deformation potentials and phonon energies previously reported<sup>6</sup> (Ref. [16] in the main text). The electron energy bands in the K- and Q-valleys are analytically captured by effective masses and non-parabolicity parameters (described in the main text, with more details provided below), and treating the Q-K energy separation ( $E_{QK}$ ) as an input parameter affected by strain. Simulations track individual electrons (in the Single-Particle Monte Carlo Method) and, similar to the Ensemble Monte Carlo Method, good statistics can be collected when the simulation is run for a sufficiently long time. As in the earlier Si work, self-heating is incorporated here by tracking the energy exchange between the electrons and lattice, such that Joule heating is the sum of all phonon energies emitted minus those absorbed, per unit time. Going beyond the earlier Si work, we estimate the temperature rise ( $\Delta T$ ) during device operation for a specific carrier density, as  $\Delta T = PR_{th}$ , where  $P$  is the power dissipated and  $R_{th}$  is the thermal resistance of the transistor, as described in the main text.

## Section B. Monte Carlo Simulation Parameters

| Parameter                           | Symbol                             | Value                               |

|-------------------------------------|------------------------------------|-------------------------------------|

| Electron effective mass ( $m_c$ )   | $m_K$<br>$m_Q$                     | $0.48m_0$<br>$0.57m_0$              |

| Non-parabolicity                    | $\alpha$                           | $2 \text{ eV}^{-1}$                 |

| Mass density                        | $\rho$                             | $3.1 \times 10^{-6} \text{ kg/m}^2$ |

| Sound velocity                      | $v_s$                              | $6.6 \times 10^3 \text{ m/s}$       |

| Deformation potentials ( $D$ )      | $D_{ac}^{K \rightarrow K}(\Gamma)$ | 4.5 eV                              |

|                                     | $D_{op}^{K \rightarrow K}(\Gamma)$ | $5.8 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{K \rightarrow K'}(K)$     | $1.4 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{K \rightarrow K'}(K)$     | $2.0 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{K \rightarrow Q}(Q)$      | $9.3 \times 10^9 \text{ eV/m}$      |

|                                     | $D_{op}^{K \rightarrow Q}(Q)$      | $1.9 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{K \rightarrow Q}(M)$      | $4.4 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{K \rightarrow Q}(M)$      | $5.6 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow Q}(\Gamma)$ | 2.8 eV                              |

|                                     | $D_{op}^{Q \rightarrow Q}(\Gamma)$ | $7.1 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow Q'}(Q)$     | $2.1 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{Q \rightarrow Q'}(Q)$     | $4.8 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow Q'}(M)$     | $2.0 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{Q \rightarrow Q'}(M)$     | $4.0 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow Q'}(K)$     | $4.8 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{Q \rightarrow Q'}(K)$     | $6.5 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow K}(Q)$      | $1.5 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{Q \rightarrow K}(Q)$      | $2.4 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{ac}^{Q \rightarrow K}(M)$      | $4.4 \times 10^{10} \text{ eV/m}$   |

|                                     | $D_{op}^{Q \rightarrow K}(M)$      | $6.6 \times 10^{10} \text{ eV/m}$   |

| Phonon energies ( $E_{\text{ph}}$ ) | $E_{\text{op}}(\Gamma)$            | 49.5 meV                            |

|                                     | $E_{\text{ac}}(K)$                 | 26.1 meV                            |

|                                     | $E_{\text{op}}(K)$                 | 46.8 meV                            |

|                                     | $E_{\text{ac}}(Q)$                 | 20.8 meV                            |

|                                     | $E_{\text{op}}(Q)$                 | 48.1 meV                            |

|                                     | $E_{\text{ac}}(M)$                 | 24.2 meV                            |

|                                     | $E_{\text{op}}(M)$                 | 47.5 meV                            |

**Table S1.** For the deformation potentials ( $D$ ), the superscript denotes the electron transition. The intravalley scattering transitions are  $K \rightarrow K$  and  $Q \rightarrow Q$ . For intervalley scattering, primed final valleys denote scattering between degenerate valleys ( $K \rightarrow K'$  and  $Q \rightarrow Q'$ ). The subscript denotes the type of phonon involved in the transition ('op' for optical and 'ac' for acoustic). The momentum of the phonon involved in the transition is specified in parentheses. For the phonon energies ( $E_{\text{ph}}$ ), the subscript denotes the type of phonon, and the phonon momentum is specified in parentheses. Deformation potentials and phonon energies are from [6] (Ref. [16] in the main text). The electron rest mass is  $m_0$ .

### Section C. Electron-Phonon Scattering Rates

Eq (1) gives the *intravalley* acoustic phonon scattering rate<sup>6</sup>:

$$\frac{1}{\tau_1} = \frac{m_c D^2 k_B T}{\hbar^3 \rho v_g^2}. \quad (1)$$

Here,  $k_B$  is the Boltzmann constant,  $T$  is the absolute temperature,  $\hbar$  is the reduced Planck constant, and the deformation potential  $D$ , as well as other inputs, are defined in **Table S1** above.

Eq (2) gives the *intravalley* optical phonon scattering rate as well as the *intervalley* (both acoustic and optical phonon) scattering rates.<sup>6</sup> These scattering rates have an energy dependence through the onset of phonon absorption and emission in the brackets, and the  $\Delta E_{QK}$  valley separation:

$$\frac{1}{\tau_2} = \frac{g_d m_c D^2}{2 \hbar \rho E_{ph}} [N_{ph} \Delta_1 + (N_{ph} + 1) \Delta_2]. \quad (2)$$

Here  $g_d$  is the degeneracy of the final valley,  $E_{ph} = \hbar \omega_{ph}$  is the phonon energy (from **Table S1**), and  $N_{ph} = \{\exp[E_{ph}/(k_B T)] - 1\}^{-1}$  is the phonon occupation. In Eq (2), the first term in the brackets corresponds to phonon absorption and the second term corresponds to phonon emission, where  $\Delta_1$  and  $\Delta_2$  are Heaviside functions including the energy onset of phonon absorption and emission, respectively. When the intervalley separation  $\Delta E_{QK}$  changes (e.g. due to strain), the scattering rates in Eq (2) are modified by adjusting  $\Delta_1$  and  $\Delta_2$ .

For example, for an electron scattering between  $K \rightarrow Q$  valleys by phonon *absorption*, scattering can only occur when  $E + E_{ph} > \Delta E_{QK}$ , where  $E$  is the electron energy with respect to the  $K$  valley. This condition is accounted for by adjusting the Heaviside function in Eq (2) such that  $\Delta_1 = \Theta(E - \Delta E_{QK} + E_{ph})$ . Similarly, for  $K \rightarrow Q$  valley scattering by phonon *emission*,  $\Delta_2 = \Theta(E - \Delta E_{QK} - E_{ph})$ . The Heaviside functions for other electron transitions can be similarly constructed.

### Section D. The Role of Band Non-Parabolicity

**Figure S1.** Monte Carlo simulation of phonon-limited drift velocity vs. electric field in monolayer MoS<sub>2</sub>, for different  $\Delta E_{QK}$  at 300 K considering a non-parabolicity factor of (a)  $\alpha = 1 \text{ eV}^{-1}$  and (b)  $\alpha = 2 \text{ eV}^{-1}$ , where (b) is reproduced from **Fig. 2c** in the main text. The  $\Delta E_{QK}$  labels in (b) apply to both plots, which share the same color scheme.

As  $\alpha$  increases, the electron effective mass  $m_{eff} = m_c(1+2\alpha E)$  grows more rapidly with energy resulting in a heavier effective mass that reduces the electron group velocity  $v_g$ , which is given in Eq (3). This

results in  $\sim 8\%$  larger high-field drift velocity in **Figure S1(a)**, where  $\alpha$  is reduced to  $1 \text{ eV}^{-1}$ , compared to **Figure S1(b)**.

$$v_g(E) = \sqrt{\frac{2E}{m_c}} \sqrt{\frac{1+\alpha E}{1+4\alpha E(1+\alpha E)}} \quad (3)$$

### Section E. Lateral Heat Dissipation

We note there are multiple length scales for the electronic and thermal behavior of transistors based on 2D semiconductors. These are roughly separated by the electron mean free path in monolayer MoS<sub>2</sub> (2-5 nm), the phonon mean free path<sup>7</sup> in monolayer MoS<sub>2</sub> ( $\sim 100$  nm), the electrostatic scale length<sup>8</sup> [ $\approx (\epsilon_{\text{ch}} t_{\text{ch}} t_{\text{ox}} / \epsilon_{\text{ox}})^{1/2}$ ], and the thermal healing length [ $L_{\text{H}}$ , eq. (5) below]. Here,  $\epsilon$  and  $t$  are the permittivity and thickness of the respective material layer, and the subscripts ‘ch’ and ‘ox’ refer to the MoS<sub>2</sub> channel and gate oxide, respectively. The electrical and thermal contact resistance<sup>7,9</sup> (between MoS<sub>2</sub> channel and metal contacts) can also influence heat generation and heat spreading, respectively.

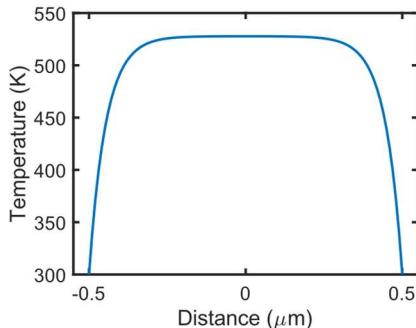

In the main text of our manuscript (**Figure 3a**), we used the simplest thermal resistance model for long-channel devices, which accounts only for heat dissipation to the substrate. This is sufficient for channel lengths  $L \gg 3L_{\text{H}}$ . At shorter channel lengths, heat dissipation to the contacts can be captured as a first approximation (under steady-state conditions) by assuming perfect heat sinking at the source and drain [ $T(\pm L/2) = T_0$ , where  $L$  is the channel length], and the temperature profile<sup>10</sup> is given by:

$$T(x) = T_0 + PR_{\text{th}} \left( 1 - \frac{\cosh\left(\frac{x}{L_{\text{H}}}\right)}{\cosh\left(\frac{L}{2L_{\text{H}}}\right)} \right) \quad (4)$$

$$L_{\text{H}} = \sqrt{R_{\text{th}} k_{\text{ch}} t_{\text{ch}}} \quad (5)$$

Here,  $P$  is the area-normalized power density [=  $I_D V_{\text{DS}} / (LW)$  if the electrical contact resistance,  $R_{\text{C}}$ , can be neglected, and  $W$  is the channel width],  $R_{\text{th}}$  is the area-normalized (vertical) thermal resistance,  $k_{\text{ch}}$  is the in-plane thermal conductivity of monolayer MoS<sub>2</sub> on an SiO<sub>2</sub> substrate,<sup>7</sup>  $t_{\text{ch}}$  is the thickness of monolayer MoS<sub>2</sub>, and  $x$  is the distance along the channel, with the channel midpoint at  $x = 0$ .

The temperature profile along a 1  $\mu\text{m}$  long channel and the relevant parameters are shown in **Figure S2**. Here,  $R_{\text{th}}$  is the thermal resistance of the MoS<sub>2</sub> channel used in the main text (including the MoS<sub>2</sub>-SiO<sub>2</sub> thermal boundary resistance, the thermal resistance of 90 nm of SiO<sub>2</sub>, and a small thermal spreading resistance into the Si substrate) and  $P$  is the power density in **Figure 3b** in the main text.

| Parameter       | Value                                       |

|-----------------|---------------------------------------------|

| $T_0$           | 300 K                                       |

| $P$             | 1.7 mW/ $\mu\text{m}^2$                     |

| $R_{\text{th}}$ | $1.34 \times 10^{-7} \text{ m}^2\text{K/W}$ |

| $L$             | 1 $\mu\text{m}$                             |

| $k_{\text{ch}}$ | 33 $\text{W m}^{-1}\text{K}^{-1}$           |

| $t_{\text{ch}}$ | $6.15 \times 10^{-10} \text{ m}$            |

**Figure S2.** (Left) Estimated temperature profile  $T(x)$  along a 1  $\mu\text{m}$  long monolayer MoS<sub>2</sub> transistor, with ‘lateral’ heat dissipation to the metal contacts (here, assumed to be perfect heat sinks) and ‘vertical’ heat dissipation to the substrate, as described in the main text. (Right) Table listing the parameters used. Other scenarios where the electrical and thermal contact resistance were included in nanomaterial devices have been treated by Pop, Liao, and Gabourie.<sup>7,11,12</sup>

We note that  $k_{\text{ch}}$  above was slightly modified (from its value for ‘long’ monolayer MoS<sub>2</sub> on SiO<sub>2</sub>) based on the work of Gabourie *et al.*<sup>7</sup> for a 1  $\mu\text{m}$  channel, and can be further reduced in shorter channels,<sup>7</sup> to account for quasi-ballistic heat flow. This simple model estimates  $L_{\text{H}} \approx 52$  nm for the geometry considered here, which is the lateral length scale of heat sinking from the channel into the metal contacts (seen as the ‘drop’ in temperature near the contacts in **Figure S2**). This signifies that for channel lengths of even  $\sim 0.25$   $\mu\text{m}$  and above, the simpler model in the main text (which includes only ‘vertical’ heat sinking) is sufficient to estimate the average temperature of the MoS<sub>2</sub> channel.

For shorter-channel devices, especially those shorter than  $L_{\text{H}}$ , numerous complexities appear, including the thermal resistance of the contacts themselves<sup>7,11,12</sup> and a non-uniform heat generation profile, which depends on the electrostatic scale length and the transistor operating regime (i.e. linear vs. saturation). In sub-10 nm channel devices there are also quasi-ballistic electron transport effects, which are natively captured by the Monte Carlo simulation, but must be self-consistently coupled with a similar treatment of phonons,<sup>4,13</sup> a task which is the subject of future work. Outside the transistor channel, the device geometry and layout ultimately determine how heat is spread, which can be described with three-dimensional finite-element thermal simulations.<sup>14</sup> For simpler geometries, this heat spreading term can be reduced to an effective  $R_{\text{th}}$ , as we have done in **Figure 3a** of our main manuscript text.

### **Supporting Information References:**

- (1) Pop, E.; Dutton, R. W.; Goodson, K. E. Monte Carlo Simulation of Joule Heating in Bulk and Strained Silicon. *Applied Physics Letters* **2005**, *86* (8), 082101. <https://doi.org/10.1063/1.1870106>.

- (2) Pop, E.; Dutton, R. W.; Goodson, K. E. Analytic Band Monte Carlo Model for Electron Transport in Si Including Acoustic and Optical Phonon Dispersion. *Journal of Applied Physics* **2004**, *96* (9), 4998–5005. <https://doi.org/10.1063/1.1788838>.

- (3) Jacoboni, C.; Reggiani, L. The Monte Carlo Method for the Solution of Charge Transport in Semiconductors with Applications to Covalent Materials. *Rev. Mod. Phys.* **1983**, *55* (3), 645–705. <https://doi.org/10.1103/RevModPhys.55.645>.

- (4) Rowlette, J. A.; Goodson, K. E. Fully Coupled Nonequilibrium Electron–Phonon Transport in Nanometer-Scale Silicon FETs. *IEEE Trans. Electron Devices* **2008**, *55* (1), 220–232. <https://doi.org/10.1109/TED.2007.911043>.

(5) Raleva, K.; Vasileska, D.; Goodnick, S. M.; Nedjalkov, M. Modeling Thermal Effects in Nanodevices. *IEEE Trans. Electron Devices* **2008**, *55* (6), 1306–1316. <https://doi.org/10.1109/TED.2008.921263>.

(6) Li, X.; Mullen, J. T.; Jin, Z.; Borysenko, K. M.; Buongiorno Nardelli, M.; Kim, K. W. Intrinsic Electrical Transport Properties of Monolayer Silicene and MoS<sub>2</sub> from First Principles. *Phys. Rev. B* **2013**, *87* (11), 115418. <https://doi.org/10.1103/PhysRevB.87.115418>.

(7) Gabourie, A. J.; Köroğlu, Ç.; Pop, E. Substrate-Dependence of Monolayer MoS<sub>2</sub> Thermal Conductivity and Thermal Boundary Conductance. *Journal of Applied Physics* **2022**, *131* (19), 195103. <https://doi.org/10.1063/5.0089247>.

(8) Das, S.; Sebastian, A.; Pop, E.; McClellan, C. J.; Franklin, A. D.; Grasser, T.; Knobloch, T.; Illarionov, Y.; Penumatcha, A. V.; Appenzeller, J.; Chen, Z.; Zhu, W.; Asselberghs, I.; Li, L.-J.; Avci, U. E.; Bhat, N.; Anthopoulos, T. D.; Singh, R. Transistors Based on Two-Dimensional Materials for Future Integrated Circuits. *Nat Electron* **2021**, *4* (11), 786–799. <https://doi.org/10.1038/s41928-021-00670-1>.

(9) English, C. D.; Shine, G.; Dorgan, V. E.; Saraswat, K. C.; Pop, E. Improved Contacts to MoS<sub>2</sub> Transistors by Ultra-High Vacuum Metal Deposition. *Nano Lett.* **2016**, *16* (6), 3824–3830. <https://doi.org/10.1021/acs.nanolett.6b01309>.

(10) Smithe, K. K. H.; English, C. D.; Suryavanshi, S. V.; Pop, E. High-Field Transport and Velocity Saturation in Synthetic Monolayer MoS<sub>2</sub>. *Nano Lett.* **2018**, *18* (7), 4516–4522. <https://doi.org/10.1021/acs.nanolett.8b01692>.

(11) Liao, A. D.; Wu, J. Z.; Wang, X.; Tahy, K.; Jena, D.; Dai, H.; Pop, E. Thermally Limited Current Carrying Ability of Graphene Nanoribbons. *Phys. Rev. Lett.* **2011**, *106* (25), 256801. <https://doi.org/10.1103/PhysRevLett.106.256801>.

(12) Pop, E. The Role of Electrical and Thermal Contact Resistance for Joule Breakdown of Single-Wall Carbon Nanotubes. *Nanotechnology* **2008**, *19* (29), 295202. <https://doi.org/10.1088/0957-4484/19/29/295202>.

(13) Gabourie, A. J.; Polanco, C. A.; McClellan, C. J.; Su, H.; Malakoutian, M.; Köroğlu, Ç.; Chowdhury, S.; Donadio, D.; Pop, E. AI-Accelerated Atoms-to-Circuits Thermal Simulation Pipeline for Integrated Circuit Design. *IEEE International Electron Devices Meeting* **2024**.

(14) Köroğlu, Ç.; Pop, E. High Thermal Conductivity Insulators for Thermal Management in 3D Integrated Circuits. *IEEE Electron Device Lett.* **2023**, *44* (3), 496–499. <https://doi.org/10.1109/LED.2023.3240676>.